# Low Noise, Precision Operational Amplifier

Data Sheet OP27

#### **FEATURES**

Low noise: 80 nV p-p (0.1 Hz to 10 Hz), 3 nV/ $\sqrt{\text{Hz}}$

Low drift: 0.2 μV/°C

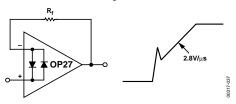

High speed: 2.8 V/ $\mu s$  slew rate, 8 MHz gain bandwidth

Low Vos: 10 µV

CMRR: 126 dB at VCM of ±11 V High open-loop gain: 1.8 million

Available in die form

### **GENERAL DESCRIPTION**

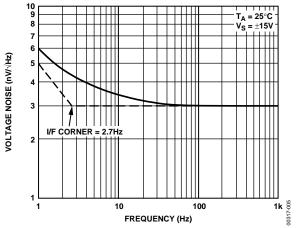

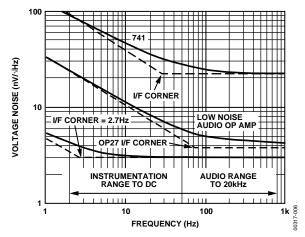

The OP27 precision operational amplifier combines the low offset and drift of the OP07 with both high speed and low noise. Offsets down to 25  $\mu V$  and maximum drift of 0.6  $\mu V/^{\circ}C$  make the OP27 ideal for precision instrumentation applications. Low noise,  $e_n=3.5~nV/\sqrt{Hz}$ , at 10 Hz, a low 1/f noise corner frequency of 2.7 Hz, and high gain (1.8 million), allow accurate high-gain amplification of low-level signals. A gain bandwidth product of 8 MHz and a 2.8 V/ $\mu$ s slew rate provide excellent dynamic accuracy in high speed, data-acquisition systems.

A low input bias current of  $\pm 10$  nA is achieved by use of a bias current cancellation circuit. Over the military temperature range, this circuit typically holds  $I_B$  and  $I_{OS}$  to  $\pm 20$  nA and 15 nA, respectively.

The output stage has good load driving capability. A guaranteed swing of  $\pm 10$  V into  $600~\Omega$  and low output distortion make the OP27 an excellent choice for professional audio applications.

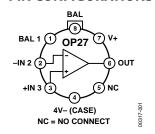

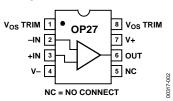

#### **PIN CONFIGURATIONS**

Figure 1. 8-Lead TO-99 (J-Suffix)

Figure 2. 8-Lead CERDIP – Glass Hermetic Seal (Z-Suffix), 8-Lead PDIP (P-Suffix), and 8-Lead SOIC (S-Suffix)

(Continued on Page 3)

#### **FUNCTIONAL BLOCK DIAGRAM** $(\mathbf{V})$ C2 R4 R3 022 046 V<sub>OS</sub> ADJ. R23 R24 R21 R1 023 Q20 Q19 Q2B Q2A OUTPUT NONINVERTING INPUT (+) Q26 INVERTING Q11 INPUT (-) Q2 Q28 <sup>1</sup>R1 AND R2 ARE PERMANENTLY ADJUSTED AT WAFER TEST FOR MINIMUM OFFSET VOLTAGE ♥ Figure 3.

Trademarks and registered trademarks are the property of their respective owners.

| TABLE OF CONTENTS                                            |                                            |    |

|--------------------------------------------------------------|--------------------------------------------|----|

| Features1                                                    | Typical Performance Characteristics        | 8  |

| General Description1                                         | Applications Information                   | 14 |

| Pin Configurations                                           | Offset Voltage Adjustment                  | 14 |

| Functional Block Diagram 1                                   | Noise Measurements                         |    |

| Revision History                                             | Unity-Gain Buffer Applications             |    |

| Specifications                                               | Comments On Noise                          |    |

| -                                                            |                                            |    |

| Electrical Characteristics                                   | Audio Applications                         |    |

| Typical Electrical Characteristics6                          | References                                 | 18 |

| Absolute Maximum Ratings7                                    | Outline Dimensions                         | 19 |

| Thermal Resistance                                           | Ordering Guide                             | 21 |

| ESD Caution                                                  |                                            |    |

| REVISION HISTORY                                             |                                            |    |

| 10/15—Rev. G to Rev. H                                       | 1/03—Rev. B to Rev. C                      |    |

| Changes to Features Section and General Description Section1 | Edits to Pin Connections                   |    |

| Changes to Note 1, Ordering Guide21                          | Edits to General Description               |    |

|                                                              | Edits to Die Characteristics               |    |

| 3/15—Rev. F to Rev. G                                        | Edits to Absolute Maximum Ratings          |    |

| Changes to General Description Section                       | Updated Outline Dimensions                 |    |

| Changes to Figure 31                                         | Edits to Figure 8                          |    |

| Changes to Applications Information Section and Output       | Edits to Outline Dimensions                | 16 |

| Voltage Adjustment Section                                   |                                            |    |

| Updated Outline Dimensions                                   | 9/01—Rev. 0 to Rev. A                      |    |

| Changes to Ordering Guide                                    | Edits to Ordering Information              |    |

|                                                              | Edits to Pin Connections                   |    |

| 5/06—Rev. E to Rev. F                                        | Edits to Absolute Maximum Ratings          |    |

| Removed References to 745Universal                           | Edits to Package Type                      |    |

| Updated 741 to AD741Universal                                | Edits to Electrical Characteristics        |    |

| Changes to Ordering Guide                                    | Edits to Wafer Test Limits                 |    |

|                                                              | Deleted Typical Electrical Characteristics |    |

| 12/05—Rev. D to Rev. E                                       | Edits to Burn-In Circuit Figure            |    |

| Edits to Figure 2                                            | Edits to Application Information           |    |

| 9/05—Rev. C to Rev. D                                        |                                            |    |

| Updated Format                                               |                                            |    |

| Changes to Table 14                                          |                                            |    |

| Removed Die Characteristics Figure5                          |                                            |    |

| Removed Wafer Test Limits Table                              |                                            |    |

| Changes to Table 5                                           |                                            |    |

| Changes to Comments on Noise Section                         |                                            |    |

### **GENERAL DESCRIPTION**

(Continued from Page 1)

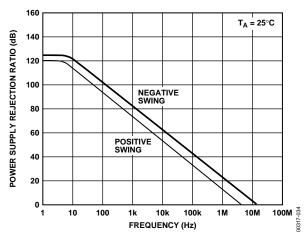

PSRR and CMRR exceed 120 dB. These characteristics, coupled with long-term drift of 0.2  $\mu V/month,$  allow the circuit designer to achieve performance levels previously attained only by discrete designs.

Low cost, high volume production of OP27 is achieved by using an on-chip Zener zap-trimming network. This reliable and stable offset trimming scheme has proven its effectiveness over many years of production history.

The OP27 provides excellent performance in low noise, high accuracy amplification of low level signals. Applications include stable integrators, precision summing amplifiers, precision voltage threshold detectors, comparators, and professional audio circuits such as tape heads and microphone preamplifiers.

# **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS**

$V_S = \pm 15$  V,  $T_A = 25$ °C, unless otherwise noted.

Table 1.

|                                                     |                       |                                                     | OP27A/OP27E |       |      | OP27G |       |      |                   |

|-----------------------------------------------------|-----------------------|-----------------------------------------------------|-------------|-------|------|-------|-------|------|-------------------|

| Parameter                                           | Symbol                | <b>Test Conditions</b>                              | Min         | Тур   | Max  | Min   | Тур   | Max  | Unit              |

| INPUT OFFSET VOLTAGE <sup>1</sup>                   | Vos                   |                                                     |             | 10    | 25   |       | 30    | 100  | μV                |

| LONG-TERM V <sub>OS</sub> STABILITY <sup>2, 3</sup> | V <sub>os</sub> /Time |                                                     |             | 0.2   | 1.0  |       | 0.4   | 2.0  | μV/M <sub>o</sub> |

| INPUT OFFSET CURRENT                                | los                   |                                                     |             | 7     | 35   |       | 12    | 75   | nA                |

| INPUT BIAS CURRENT                                  | I <sub>B</sub>        |                                                     |             | ±10   | ±40  |       | ±15   | ±80  | nA                |

| INPUT NOISE VOLTAGE <sup>3, 4</sup>                 | e <sub>n p-p</sub>    | 0.1 Hz to 10 Hz                                     |             | 0.08  | 0.18 |       | 0.09  | 0.25 | μV p-p            |

| INPUT NOISE                                         | e <sub>n</sub>        | $f_0 = 10 \text{ Hz}$                               |             | 3.5   | 5.5  |       | 3.8   | 8.0  | nV/√Hz            |

| Voltage Density <sup>3</sup>                        |                       | $f_0 = 30 \text{ Hz}$                               |             | 3.1   | 4.5  |       | 3.3   | 5.6  | nV/√Hz            |

|                                                     |                       | $f_0 = 1000 \text{ Hz}$                             |             | 3.0   | 3.8  |       | 3.2   | 4.5  | nV/√Hz            |

| INPUT NOISE                                         | İn                    | f <sub>0</sub> = 10 Hz                              |             | 1.7   | 4.0  |       | 1.7   |      | pA/√Hz            |

| Current Density <sup>3</sup>                        |                       | $f_0 = 30 \text{ Hz}$                               |             | 1.0   | 2.3  |       | 1.0   |      | pA/√Hz            |

|                                                     |                       | $f_0 = 1000 \text{ Hz}$                             |             | 0.4   | 0.6  |       | 0.4   | 0.6  | pA/√Hz            |

| INPUT RESISTANCE                                    |                       |                                                     |             |       |      |       |       |      |                   |

| Differential Mode <sup>5</sup>                      | R <sub>IN</sub>       |                                                     | 1.3         | 6     |      | 0.7   | 4     |      | ΜΩ                |

| Common Mode                                         | RINCM                 |                                                     |             | 3     |      |       | 2     |      | GΩ                |

| INPUT VOLTAGE RANGE                                 | IVR                   |                                                     | ±11.0       | ±12.3 |      | ±11.0 | ±12.3 |      | ٧                 |

| COMMON-MODE REJECTION RATIO                         | CMRR                  | $V_{CM} = \pm 11 \text{ V}$                         | 114         | 126   |      | 100   | 120   |      | dB                |

| POWER SUPPLY REJECTION RATIO                        | PSRR                  | $V_S = \pm 4 \text{ V to } \pm 18 \text{ V}$        |             | 1     | 10   |       | 2     | 20   | μV/V              |

| LARGE SIGNAL VOLTAGE GAIN                           | Avo                   | $R_L \ge 2 \text{ k}\Omega, V_O = \pm 10 \text{ V}$ | 1000        | 1800  |      | 700   | 1500  |      | V/mV              |

|                                                     |                       | $R_L \ge 600~\Omega, V_O = \pm 10~V$                | 800         | 1500  |      | 600   | 1500  |      | V/mV              |

| OUTPUT VOLTAGE SWING                                | Vo                    | $R_L \ge 2 k\Omega$                                 | ±12.0       | ±13.8 |      | ±11.5 | ±13.5 |      | ٧                 |

|                                                     |                       | $R_L \ge 600  \Omega$                               | ±10.0       | ±11.5 |      | ±10.0 | ±11.5 |      | V                 |

| SLEW RATE <sup>6</sup>                              | SR                    | $R_L \ge 2 k\Omega$                                 | 1.7         | 2.8   |      | 1.7   | 2.8   |      | V/µs              |

| GAIN BANDWIDTH PRODUCT <sup>6</sup>                 | GBW                   |                                                     | 5.0         | 8.0   |      | 5.0   | 8.0   |      | MHz               |

| OPEN-LOOP OUTPUT RESISTANCE                         | Ro                    | $V_0 = 0$ , $I_0 = 0$                               |             | 70    |      |       | 70    |      | Ω                 |

| POWER CONSUMPTION                                   | P <sub>d</sub>        | Vo                                                  |             | 90    | 140  |       | 100   | 170  | mW                |

| OFFSET ADJUSTMENT RANGE                             |                       | $R_P = 10 \text{ k}\Omega$                          |             | ±4.0  |      |       | ±4.0  |      | mV                |

<sup>&</sup>lt;sup>1</sup> Input offset voltage measurements are performed approximately 0.5 seconds after application of power. A/E grades guaranteed fully warmed up.

<sup>&</sup>lt;sup>2</sup> Long-term input offset voltage stability refers to the average trend line of V<sub>OS</sub> vs. time over extended periods after the first 30 days of operation. Excluding the initial hour of operation, changes in V<sub>OS</sub> during the first 30 days are typically 2.5 μV. Refer to the Typical Performance Characteristics section.

$<sup>^{\</sup>rm 3}$  Sample tested.

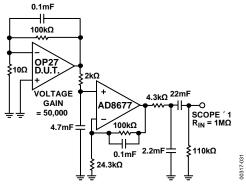

<sup>&</sup>lt;sup>4</sup> See voltage noise test circuit (Figure 31).

<sup>&</sup>lt;sup>5</sup> Guaranteed by input bias current.

<sup>&</sup>lt;sup>6</sup> Guaranteed by design.

**Data Sheet**

$V_S = \pm 15 \text{ V}, -55^{\circ}\text{C} \le T_A \le 125^{\circ}\text{C}$ , unless otherwise noted.

Table 2.

|                                   |                                 |                                                     |       | OP27A |     |       |

|-----------------------------------|---------------------------------|-----------------------------------------------------|-------|-------|-----|-------|

| Parameter                         | Symbol                          | Test Conditions                                     | Min   | Тур   | Max | Unit  |

| INPUT OFFSET VOLTAGE <sup>1</sup> | Vos                             |                                                     |       | 30    | 60  | μV    |

| AVERAGE INPUT OFFSET DRIFT        | TCV <sub>OS</sub> <sup>2</sup>  |                                                     |       |       |     |       |

|                                   | TCV <sub>OSn</sub> <sup>3</sup> |                                                     |       | 0.2   | 0.6 | μV/°C |

| INPUT OFFSET CURRENT              | los                             |                                                     |       | 15    | 50  | nA    |

| INPUT BIAS CURRENT                | IB                              |                                                     |       | ±20   | ±60 | nA    |

| INPUT VOLTAGE RANGE               | IVR                             |                                                     | ±10.3 | ±11.5 |     | ٧     |

| COMMON-MODE REJECTION RATIO       | CMRR                            | $V_{CM} = \pm 10 \text{ V}$                         | 108   | 122   |     | dB    |

| POWER SUPPLY REJECTION RATIO      | PSRR                            | $V_S = \pm 4.5 \text{ V to } \pm 18 \text{ V}$      |       | 2     | 16  | μV/V  |

| LARGE SIGNAL VOLTAGE GAIN         | Avo                             | $R_L \ge 2 \text{ k}\Omega, V_O = \pm 10 \text{ V}$ | 600   | 1200  |     | V/mV  |

| OUTPUT VOLTAGE SWING              | Vo                              | $R_L \ge 2 \ k\Omega$                               | ±11.5 | ±13.5 |     | ٧     |

<sup>1</sup> Input offset voltage measurements are performed by automated test equipment approximately 0.5 seconds after application of power. A/E grades guaranteed fully warmed up.

$V_S = \pm 15 \text{ V}, -25^{\circ}\text{C} \le T_A \le 85^{\circ}\text{C}$  for OP27J and OP27Z and  $-40^{\circ}\text{C} \le T_A \le 85^{\circ}\text{C}$  for OP27GS, unless otherwise noted.

Table 3.

|                              |                                 |                                                     |       | OP27E |     |       | OP27G |      |       |

|------------------------------|---------------------------------|-----------------------------------------------------|-------|-------|-----|-------|-------|------|-------|

| Parameter                    | Symbol                          | <b>Test Conditions</b>                              | Min   | Тур   | Max | Min   | Тур   | Max  | Unit  |

| INPUT ONSET VOLTAGE          | Vos                             |                                                     |       | 20    | 50  |       | 55    | 220  | μV    |

| AVERAGE INPUT OFFSET DRIFT   | TCV <sub>os</sub> <sup>1</sup>  |                                                     |       | 0.2   | 0.6 |       | 0 4   | 1.8  | μV/°C |

|                              | TCV <sub>OSn</sub> <sup>2</sup> |                                                     |       | 0.2   | 0.6 |       | 0 4   | 1.8  | μV/°C |

| INPUT OFFSET CURRENT         | los                             |                                                     |       | 10    | 50  |       | 20    | 135  | nA    |

| INPUT BIAS CURRENT           | I <sub>B</sub>                  |                                                     |       | ±14   | ±60 |       | ±25   | ±150 | nA    |

| INPUT VOLTAGE RANGE          | IVR                             |                                                     | ±10.5 | ±11.8 |     | ±10.5 | ±11.8 |      | V     |

| COMMON-MODE REJECTION RATIO  | CMRR                            | $V_{CM} = \pm 10 \text{ V}$                         | 110   | 124   |     | 96    | 118   |      | dB    |

| POWER SUPPLY REJECTION RATIO | PSRR                            | $V_S = \pm 4.5 \text{ V to } \pm 18 \text{ V}$      |       | 2     | 15  |       | 2     | 32   | μV/V  |

| LARGE SIGNAL VOLTAGE GAIN    | Avo                             | $R_L \ge 2 \text{ k}\Omega, V_O = \pm 10 \text{ V}$ | 750   | 1500  |     | 450   | 1000  |      | V/mV  |

| OUTPUT VOLTAGE SWING         | Vo                              | $R_L \ge 2 \ k\Omega$                               | ±11.7 | ±13.6 |     | ±11.0 | ±13.3 |      | ٧     |

$<sup>^{1}\</sup>text{The TCV}_{OS} \text{ performance is within the specifications unnulled or when nulled with } R_{P} = 8 \text{ k}\Omega \text{ to } 20 \text{ k}\Omega. \text{ TCV}_{OS} \text{ is } 100\% \text{ tested for A/E grades, sample tested for C/G grades.}$

$<sup>^{2}</sup>$  The TCV $_{0s}$  performance is within the specifications unnulled or when nulled with  $R_{P} = 8 \text{ k}\Omega$  to  $20 \text{ k}\Omega$ . TCV $_{0s}$  is 100% tested for A/E grades, sample tested for G grades.

<sup>&</sup>lt;sup>3</sup> Guaranteed by design.

<sup>&</sup>lt;sup>2</sup> Guaranteed by design.

# TYPICAL ELECTRICAL CHARACTERISTICS

$V_S = \pm 15$  V,  $T_A = 25$ °C unless otherwise noted.

Table 4.

| Parameter                                       | Symbol            | Test Conditions                                                       | OP27N Typical | Unit   |

|-------------------------------------------------|-------------------|-----------------------------------------------------------------------|---------------|--------|

| AVERAGE INPUT OFFSET VOLTAGE DRIFT <sup>1</sup> | TCVos or TCVosn   | Nulled or unnulled, $R_P = 8 \text{ k}\Omega$ to $20 \text{ k}\Omega$ | 0.2           | μV/°C  |

| AVERAGE INPUT OFFSET CURRENT DRIFT              | TClos             |                                                                       | 80            | pA/°C  |

| AVERAGE INPUT BIAS CURRENT DRIFT                | TCI <sub>B</sub>  |                                                                       | 100           | pA/°C  |

| INPUT NOISE VOLTAGE DENSITY                     | e <sub>n</sub>    | f <sub>O</sub> = 10 Hz                                                | 3.5           | nV/√Hz |

|                                                 |                   | f <sub>0</sub> = 30 Hz                                                | 3.1           | nV/√Hz |

|                                                 |                   | f <sub>0</sub> = 1000 Hz                                              | 3.0           | nV/√Hz |

| INPUT NOISE CURRENT DENSITY                     | in                | f <sub>0</sub> = 10 Hz                                                | 1.7           | pA/√Hz |

|                                                 |                   | f <sub>0</sub> = 30 Hz                                                | 1.0           | pA/√Hz |

|                                                 |                   | f <sub>O</sub> = 1000 Hz                                              | 0.4           | pA/√Hz |

| INPUT NOISE VOLTAGE SLEW RATE                   | e <sub>np-p</sub> | 0.1 Hz to 10 Hz                                                       | 0.08          | μV p-p |

|                                                 | SR                | $R_L \ge 2 k\Omega$                                                   | 2.8           | V/µs   |

| GAIN BANDWIDTH PRODUCT                          | GBW               |                                                                       | 8             | MHz    |

$<sup>^1 \, \</sup>text{Input offset voltage measurements are performed by automated test equipment approximately 0.5 seconds after application of power.} \\$

# **ABSOLUTE MAXIMUM RATINGS**

Table 5.

| Parameter                                  | Rating          |

|--------------------------------------------|-----------------|

| Supply Voltage                             | ±22 V           |

| Input Voltage <sup>1</sup>                 | ±22 V           |

| Output Short-Circuit Duration              | Indefinite      |

| Differential Input Voltage <sup>2</sup>    | ±0.7 V          |

| Differential Input Current <sup>2</sup>    | ±25 mA          |

| Storage Temperature Range                  | −65°C to +150°C |

| Operating Temperature Range                |                 |

| OP27A (J, Z)                               | −55°C to +125°C |

| OP27E (Z)                                  | −25°C to +85°C  |

| OP27E (P)                                  | 0°C to 70°C     |

| OP27G (P, S, J, Z)                         | -40°C to +85°C  |

| Lead Temperature Range (Soldering, 60 sec) | 300°C           |

| Junction Temperature                       | −65°C to +150°C |

$<sup>^{\</sup>rm 1}$  For supply voltages less than  $\pm 22$  V, the absolute maximum input voltage is equal to the supply voltage.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is,  $\theta_{JA}$  is specified for device in socket for TO-99, CERDIP, and PDIP packages;  $\theta_{JA}$  is specified for device soldered to printed circuit board for SOIC package.

Absolute maximum ratings apply to both dice and packaged parts, unless otherwise noted.

Table 6.

| Package Type                 | θ <sub>JA</sub> | θις | Unit |

|------------------------------|-----------------|-----|------|

| 8-Lead Metal Can (TO-99) (J) | 150             | 18  | °C/W |

| 8-Lead CERDIP (Z)            | 148             | 16  | °C/W |

| 8-Lead PDIP (P)              | 103             | 43  | °C/W |

| 8-Lead SOIC_N (S)            | 158             | 43  | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$<sup>^2</sup>$ The inputs of the OP27 are protected by back-to-back diodes. Current limiting resistors are not used in order to achieve low noise. If differential input voltage exceeds  $\pm 0.7$  V, the input current should be limited to 25 mA.

# TYPICAL PERFORMANCE CHARACTERISTICS

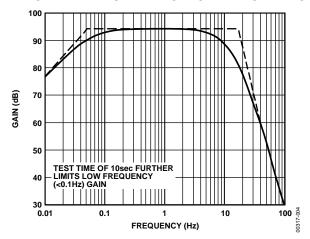

Figure 4. 0.1 Hz to 10 Hz p-p Noise Tester Frequency Response

Figure 5. Voltage Noise Density vs. Frequency

Figure 6. A Comparison of Op Amp Voltage Noise Spectra

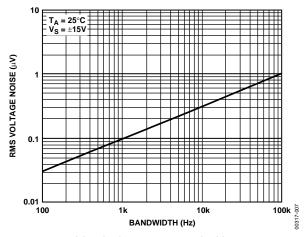

Figure 7. Input Wideband Voltage Noise vs. Bandwidth (0.1 Hz to Frequency Indicated)

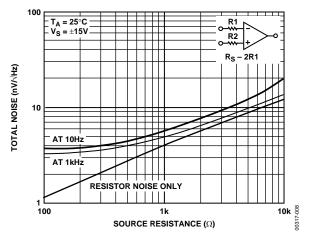

Figure 8. Total Noise vs. Sourced Resistance

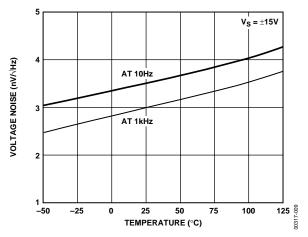

Figure 9. Voltage Noise Density vs. Temperature

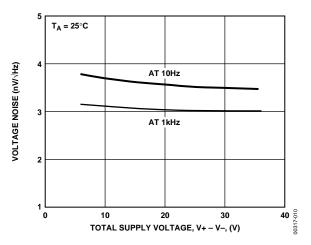

Figure 10. Voltage Noise Density vs. Supply Voltage

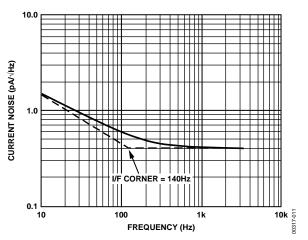

Figure 11. Current Noise Density vs. Frequency

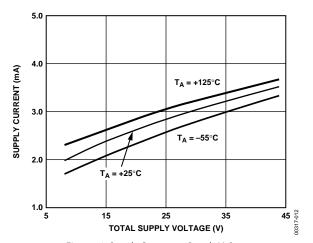

Figure 12. Supply Current vs. Supply Voltage

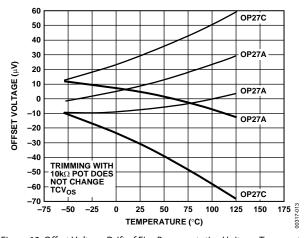

Figure 13. Offset Voltage Drift of Five Representative Units vs. Temperature

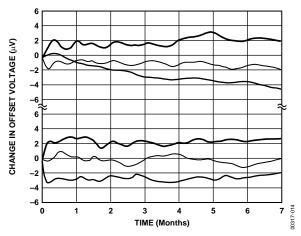

Figure 14. Long-Term Offset Voltage Drift of Six Representative Units

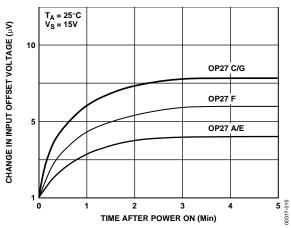

Figure 15. Warm-Up Offset Voltage Drift

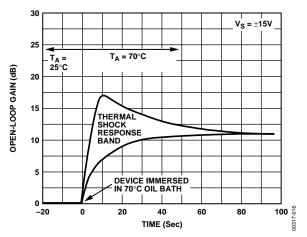

Figure 16. Offset Voltage Change Due to Thermal Shock

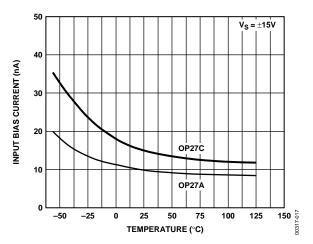

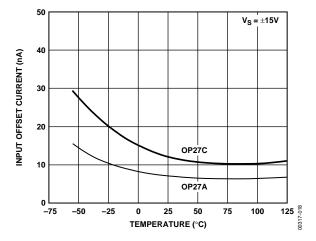

Figure 17. Input Bias Current vs. Temperature

Figure 18. Input Offset Current vs. Temperature

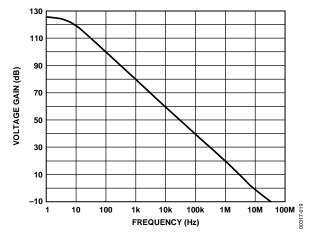

Figure 19. Open-Loop Gain vs. Frequency

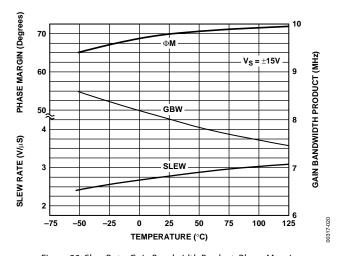

Figure 20. Slew Rate, Gain Bandwidth Product, Phase Margin vs. Temperature

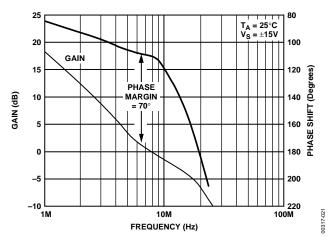

Figure 21. Gain, Phase Shift vs. Frequency

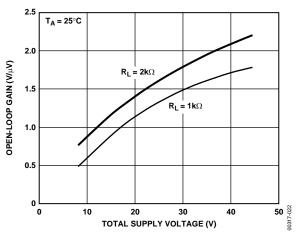

Figure 22. Open-Loop Voltage Gain vs. Supply Voltage

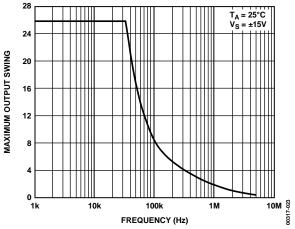

Figure 23. Maximum Output Swing vs. Frequency

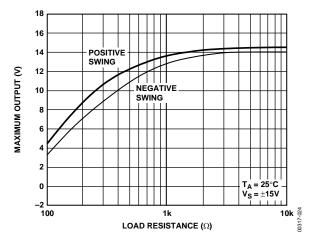

Figure 24. Maximum Output Voltage vs. Load Resistance

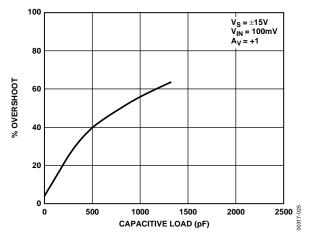

Figure 25. Small-Signal Overshoot vs. Capacitive Load

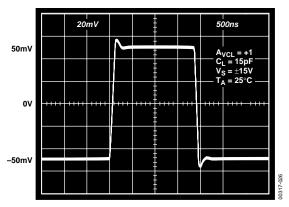

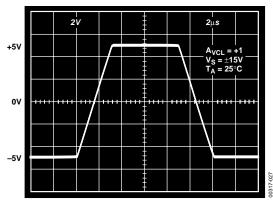

Figure 26. Small-Signal Transient Response

Figure 27. Large Signal Transient Response

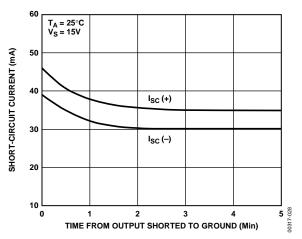

Figure 28. Short-Circuit Current vs. Time

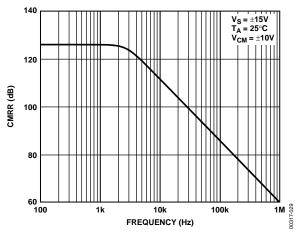

Figure 29. CMRR vs. Frequency

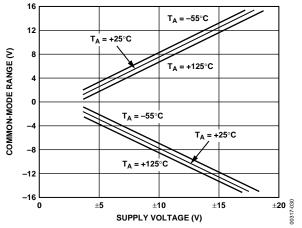

Figure 30. Common-Mode Input Range vs. Supply Voltage

Figure 31. Voltage Noise Test Circuit (0.1 Hz to 10 Hz)

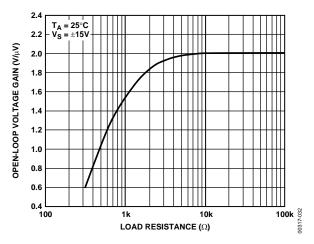

Figure 32. Open-Loop Voltage Gain vs. Load Resistance

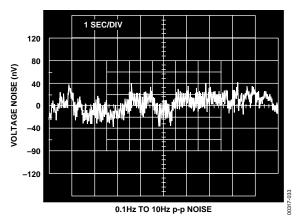

Figure 33. Low Frequency Noise

Figure 34. PSRR vs. Frequency

## APPLICATIONS INFORMATION

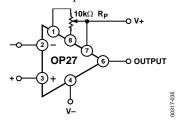

OP27 series units can be inserted directly into OP07 sockets with or without removal of external compensation or nulling components. OP27 offset voltage can be nulled to 0 (or another desired setting) using a potentiometer (see Figure 35).

The OP27 provides stable operation with load capacitances of up to 2000 pF and  $\pm 10$  V swings; larger capacitances should be decoupled with a 50  $\Omega$  resistor inside the feedback loop. The OP27 is unity-gain stable.

Thermoelectric voltages generated by dissimilar metals at the input terminal contacts can degrade the drift performance. Best operation is obtained when both input contacts are maintained at the same temperature.

Figure 35. Offset Nulling Circuit

### **OFFSET VOLTAGE ADJUSTMENT**

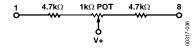

The input offset voltage of the OP27 is trimmed at wafer level. However, if further adjustment of  $V_{OS}$  is necessary, a 10 k $\Omega$  trim potentiometer can be used.  $TCV_{OS}$  is not degraded (see Figure 35). Other potentiometer values from 1 k $\Omega$  to 1 M $\Omega$  can be used with a slight degradation (0.1  $\mu V/^{\circ}C$  to 0.2  $\mu V/^{\circ}C$ ) of  $TCV_{OS}$ . Trimming to a value other than zero creates a drift of approximately ( $V_{OS}/300$ )  $\mu V/^{\circ}C$ . For example, the change in  $TCV_{OS}$  is 0.33  $\mu V/^{\circ}C$  if  $V_{OS}$  is adjusted to 100  $\mu V$ . The offset voltage adjustment range with a 10 k $\Omega$  potentiometer is  $\pm 4$  mV. If smaller adjustment range is required, the nulling sensitivity can be reduced by using a smaller potentiometer in conjunction with fixed resistors. For example, Figure 36 shows a network that has a  $\pm 280~\mu V$  adjustment range.

Figure 36. Offset Voltage Adjustment

### **NOISE MEASUREMENTS**

To measure the 80 nV p-p noise specification of the OP27 in the 0.1 Hz to 10 Hz range, the following precautions must be observed:

- The device must be warmed up for at least five minutes.

As shown in the warm-up drift curve, the offset voltage typically changes 4 μV due to increasing chip temperature after power-up. In the 10-second measurement interval, these temperature-induced effects can exceed tens-of-nanovolts.

- For similar reasons, the device has to be well-shielded from air currents. Shielding minimizes thermocouple effects.

- Sudden motion in the vicinity of the device can also feedthrough to increase the observed noise.

- The test time to measure 0.1 Hz to 10 Hz noise should not exceed 10 seconds. As shown in the noise-tester frequency response curve, the 0.1 Hz corner is defined by only one zero. The test time of 10 seconds acts as an additional zero to eliminate noise contributions from the frequency band below 0.1 Hz.

- A noise voltage density test is recommended when measuring noise on a large number of units. A 10 Hz noise voltage density measurement correlates well with a 0.1 Hz to 10 Hz p-p noise reading, since both results are determined by the white noise and the location of the 1/f corner frequency.

### **UNITY-GAIN BUFFER APPLICATIONS**

When  $R_f \le 100 \Omega$  and the input is driven with a fast, large signal pulse (>1 V), the output waveform looks as shown in the pulsed operation diagram (see Figure 37).

During the fast feedthrough-like portion of the output, the input protection diodes effectively short the output to the input, and a current, limited only by the output short-circuit protection, is drawn by the signal generator. With  $R_f \! \geq \! 500~\Omega,$  the output is capable of handling the current requirements ( $I_L \! \leq \! 20~mA$  at 10~V); the amplifier stays in its active mode and a smooth transition occurs.

When  $R_f > 2$  k $\Omega$ , a pole is created with  $R_f$  and the amplifier's input capacitance (8 pF) that creates additional phase shift and reduces phase margin. A small capacitor (20 pF to 50 pF) in parallel with  $R_f$  eliminates this problem.

Figure 37. Pulsed Operation

#### **COMMENTS ON NOISE**

The OP27 is a very low noise, monolithic op amp. The outstanding input voltage noise characteristics of the OP27 are achieved mainly by operating the input stage at a high quiescent current. The input bias and offset currents, which would normally increase, are held to reasonable values by the input bias current cancellation circuit. The OP27A/OP27E has  $I_B$  and  $I_{\rm OS}$  of only  $\pm 40$  nA and 35 nA at 25°C respectively. This is particularly important when the input has a high source resistance. In addition, many audio amplifier designers prefer to use direct coupling. The high  $I_B$ ,  $V_{\rm OS}$ , and  $TCV_{\rm OS}$  of previous designs have made direct coupling difficult, if not impossible, to use.

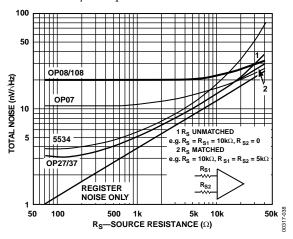

Voltage noise is inversely proportional to the square root of bias current, but current noise is proportional to the square root of bias current. The noise advantage of the OP27 disappears when high source resistors are used. Figure 38, Figure 39, Figure 40 compare the observed total noise of the OP27 with the noise performance of other devices in different circuit applications.

$$Total \, Noise = \begin{bmatrix} (Voltage \, Noise)^2 + \\ (Current \, Noise \times R_S)^2 + \\ (Resistor \, Noise)^2 \end{bmatrix}^{1/2}$$

Figure 38 shows noise vs. source resistance at 1000 Hz. The same plot applies to wideband noise. To use this plot, multiply the vertical scale by the square root of the bandwidth.

Figure 38. Noise vs. Source Resistance (Including Resistor Noise) at 1000 Hz

At  $R_S<1~k\Omega$ , the low voltage noise of the OP27 is maintained. With  $R_S<1~k\Omega$ , total noise increases but is dominated by the resistor noise rather than current or voltage noise. It is only beyond  $R_S$  of 20  $k\Omega$  that current noise starts to dominate. The argument can be made that current noise is not important for applications with low-to-moderate source resistances. The crossover between the OP27 and OP07 noise occurs in the 15  $k\Omega$  to  $40~k\Omega$  region.

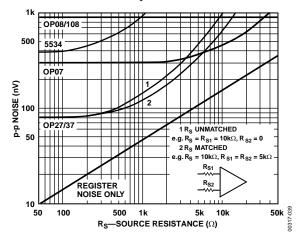

Figure 39 shows the 0.1 Hz to 10 Hz p-p noise. Here the picture is less favorable; resistor noise is negligible and current noise becomes important because it is inversely proportional to the square root of frequency. The crossover with the OP07 occurs in the 3 k $\Omega$  to 5 k $\Omega$  range depending on whether balanced or unbalanced source resistors are used (at 3 k $\Omega$  the  $I_B$  and  $I_{OS}$  error also can be 3× the  $V_{OS}$  spec).

Figure 39. Peak-to-Peak Noise (0.1 Hz to 10 Hz) as Source Resistance (Includes Resistor Noise)

For low frequency applications, the OP07 is better than the OP27/OP37 when RS > 3 k $\Omega$ . The only exception is when gain error is important.

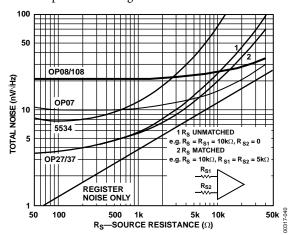

Figure 40 illustrates the 10 Hz noise. As expected, the results are between the previous two figures.

Figure 40. 10 Hz Noise vs. Source Resistance (Includes Resistor Noise) Audio Applications

For reference, typical source resistances of some signal sources are listed in Table 7.

Table 7.

| Device                                            | Source<br>Impedance | Comments                                                                                                                     |

|---------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------|

| Strain Gauge                                      | <500 Ω              | Typically used in low frequency applications.                                                                                |

| Magnetic<br>Tape Head                             | <1500 Ω             | Low is very important to reduce self-magnetization problems when direct coupling is used.  OP27 IB can be neglected.         |

| Magnetic<br>Phonograph<br>Cartridges              | <1500 Ω             | Similar need for low I <sub>B</sub> in direct coupled applications. OP27 does not introduce any self-magnetization problems. |

| Linear<br>Variable<br>Differential<br>Transformer | <1500 Ω             | Used in rugged servo-feedback applications. Bandwidth of interest is 400 Hz to 5 kHz.                                        |

Table 8. Open-Loop Gain

| Frequency | OP07   | OP27   | OP37   |

|-----------|--------|--------|--------|

| At 3 Hz   | 100 dB | 124 dB | 125 dB |

| At 10 Hz  | 100 dB | 120 dB | 125 dB |

| At 30 Hz  | 90 dB  | 110 dB | 124 dB |

### **AUDIO APPLICATIONS**

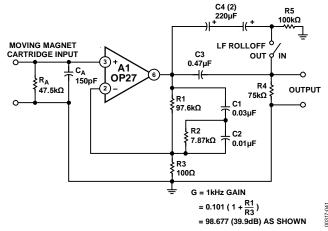

Figure 41 is an example of a phono pre-amplifier circuit using the OP27 for A1; R1-R2-C1-C2 form a very accurate RIAA network with standard component values. The popular method to accomplish RIAA phono equalization is to employ frequency dependent feedback around a high quality gain block. Properly chosen, an RC network can provide the three necessary time constants of 3180  $\mu s$ , 318  $\mu s$ , and 75  $\mu s$ .

For initial equalization accuracy and stability, precision metal film resistors and film capacitors of polystyrene or polypropylene are recommended because they have low voltage coefficients, dissipation factors, and dielectric absorption. (High-k ceramic capacitors should be avoided here, though low-k ceramics, such as NPO types that have excellent dissipation factors and somewhat lower dielectric absorption, can be considered for small values.)

Figure 41. Phono Preamplifier Circuit

The OP27 brings a 3.2 nV/ $\sqrt{\text{Hz}}$  voltage noise and 0.45 pA/ $\sqrt{\text{Hz}}$  current noise to this circuit. To minimize noise from other sources, R3 is set to a value of 100  $\Omega$ , generating a voltage noise of 1.3 nV/ $\sqrt{\text{Hz}}$ . The noise increases the 3.2 nV/ $\sqrt{\text{Hz}}$  of the amplifier by only 0.7 dB. With a 1 k $\Omega$  source, the circuit noise measures 63 dB below a 1 mV reference level, unweighted, in a 20 kHz noise bandwidth.

Gain (G) of the circuit at 1 kHz can be calculated by the expression:

$$G = 0.101 \left( 1 + \frac{R1}{R3} \right)$$

For the values shown, the gain is just under 100 (or 40 dB). Lower gains can be accommodated by increasing R3, but gains higher than 40 dB show more equalization errors because of the 8 MHz gain bandwidth of the OP27.

This circuit is capable of very low distortion over its entire range, generally below 0.01% at levels up to 7 V rms. At 3 V output levels, it produces less than 0.03% total harmonic distortion at frequencies up to 20 kHz.

Capacitor C3 and Resistor R4 form a simple –6 dB per octave rumble filter, with a corner at 22 Hz. As an option, the switch selected Shunt Capacitor C4, a nonpolarized electrolytic, bypasses the low frequency roll-off. Placing the rumble filter's high-pass action after the preamplifier has the desirable result of discriminating against the RIAA-amplified low frequency noise components and pickup produced low frequency disturbances.

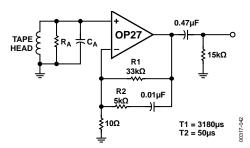

A preamplifier for NAB tape playback is similar to an RIAA phono preamplifier, though more gain is typically demanded, along with equalization requiring a heavy low frequency boost. The circuit in Figure 41 can be readily modified for tape use, as shown by Figure 42.

Figure 42. Tape Head Preamplifier

While the tape equalization requirement has a flat high frequency gain above 3 kHz ( $T2 = 50 \mu s$ ), the amplifier need not be stabilized for unity gain. The decompensated OP37 provides a greater bandwidth and slew rate. For many applications, the idealized time constants shown can require trimming of R1 and R2 to optimize frequency response for nonideal tape head performance and other factors (see the References section).

The network values of the configuration yield a 50 dB gain at 1 kHz, and the dc gain is greater than 70 dB. Thus, the worst-case output offset is just over 500 mV. A single 0.47  $\mu F$  output capacitor can block this level without affecting the dynamic range.

The tape head can be coupled directly to the amplifier input, because the worst-case bias current of 80 nA with a 400 mH,  $100 \mu$  inch head (such as the PRB2H7K) is not troublesome.

Amplifier bias-current transients that can magnetize a head present one potential tape head problem. The OP27 and OP37 are free of bias current transients upon power-up or power-down. It is always advantageous to control the speed of power supply rise and fall to eliminate transients.

In addition, the dc resistance of the head should be carefully controlled and preferably below 1 k $\Omega$ . For this configuration, the bias current induced offset voltage can be greater than the 100 pV maximum offset if the head resistance is not sufficiently controlled.

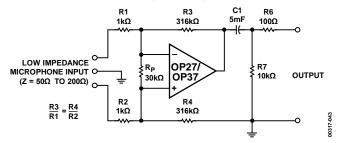

A simple, but effective, fixed gain transformerless microphone preamp (Figure 43) amplifies differential signals from low impedance microphones by 50 dB and has an input impedance of 2 k $\Omega$ . Because of the high working gain of the circuit, an OP37 helps to preserve bandwidth, which is 110 kHz. As the OP37 is a decompensated device (minimum stable gain of 5), a dummy resistor,  $R_p$ , may be necessary if the microphone is to be unplugged. Otherwise, the 100% feedback from the open input can cause the amplifier to oscillate.

Common-mode input noise rejection will depend upon the match of the bridge-resistor ratios. Either close tolerance (0.1%) types should be used, or R4 should be trimmed for best CMRR. All resistors should be metal film types for best stability and low noise.

Noise performance of this circuit is limited more by the Input Resistors R1 and R2 than by the op amp, as R1 and R2 each generate a  $4 \text{ nV}/\sqrt{\text{Hz}}$  noise, while the op amp generates a  $3.2 \text{ nV}/\sqrt{\text{Hz}}$  noise. The rms sum of these predominant noise

sources is about 6 nV/ $\sqrt{\text{Hz}}$ , equivalent to 0.9  $\mu\text{V}$  in a 20 kHz noise bandwidth, or nearly 61 dB below a 1 mV input signal. Measurements confirm this predicted performance.

Figure 43. Fixed Gain Transformerless Microphone Preamplifier

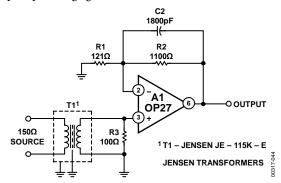

For applications demanding appreciably lower noise, a high quality microphone transformer coupled preamplifier (Figure 44) incorporates the internally compensated OP27. T1 is a JE-115K-E 150  $\Omega/15$  k $\Omega$  transformer that provides an optimum source resistance for the OP27 device. The circuit has an overall gain of 40 dB, the product of the transformer's voltage setup and the op amp's voltage gain.

Figure 44. High Quality Microphone Transformer Coupled Preamplifier

Gain can be trimmed to other levels, if desired, by adjusting R2 or R1. Because of the low offset voltage of the OP27, the output offset of this circuit is very low, 1.7 mV or less, for a 40 dB gain. The typical output blocking capacitor can be eliminated in such cases, but it is desirable for higher gains to eliminate switching transients.

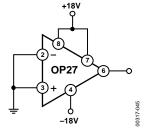

Figure 45. Burn-In Circuit

Capacitor C2 and Resistor R2 form a 2  $\mu$ s time constant in this circuit, as recommended for optimum transient response by the transformer manufacturer. With C2 in use, A1 must have unitygain stability. For situations where the 2  $\mu$ s time constant is not necessary, C2 can be deleted, allowing the faster OP37 to be employed.

A 150  $\Omega$  resistor and R1 and R2 gain resistors connected to a noiseless amplifier generate 220 nV of noise in a 20 kHz bandwidth, or 73 dB below a 1 mV reference level. Any practical amplifier can only approach this noise level; it can never exceed it. With the OP27 and T1 specified, the additional noise degradation is close to 3.6 dB (or –69.5 referenced to 1 mV).

### **REFERENCES**

- 1. Lipshitz, S. R, "On RIAA Equalization Networks," JAES, Vol. 27, June 1979, p. 458–481.

- 2. Jung, W. G., *IC Op Amp Cookbook*, 2nd. Ed., H. W. Sams and Company, 1980.

- 3. Jung, W. G., *Audio IC Op Amp Applications*, 2nd. Ed., H. W. Sams and Company, 1978.

- 4. Jung, W. G., and Marsh, R. M., "Picking Capacitors," *Audio*, February and March, 1980.

- 5. Otala, M., "Feedback-Generated Phase Nonlinearity in Audio Amplifiers," London AES Convention, March 1980, preprint 1976.

- 6. Stout, D. F., and Kaufman, M., *Handbook of Operational Amplifier Circuit Design*, New York, McGraw-Hill, 1976.

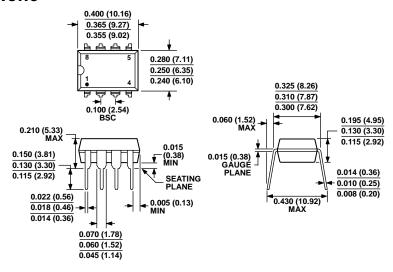

# **OUTLINE DIMENSIONS**

#### **COMPLIANT TO JEDEC STANDARDS MS-001**

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 46. 8-Lead Plastic Dual-in-Line Package [PDIP] (N-8) P-Suffix

Dimensions shown in inches and (millimeters)

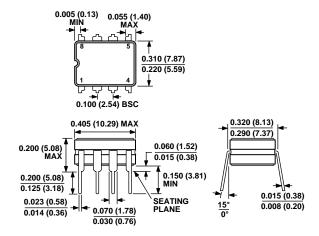

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 47. 8-Lead Ceramic DIP – Glass Hermetic Seal [CERDIP] (Q-8) Z-Suffix

Dimensions shown in inches and (millimeters)

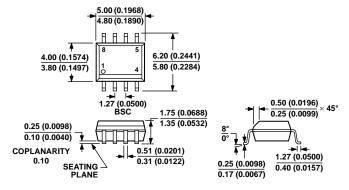

COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 48. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

S-Suffix

Dimensions shown in millimeters and (inches)

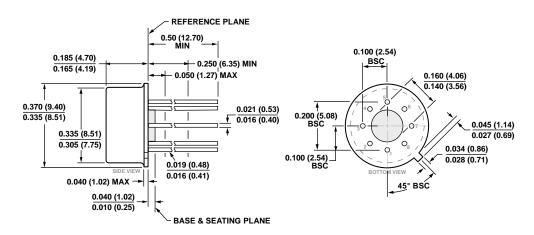

COMPLIANT TO JEDEC STANDARDS MO-002-AK

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 49. 8-Lead Metal Can [TO-99] (H-08) J-Suffix

Dimensions shown in inches and (millimeters)

Rev. H | Page 20 of 21

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description      | Package Option  |

|--------------------|-------------------|--------------------------|-----------------|

| OP27AJ/883C        | −55°C to +125°C   | 8-Lead Metal Can (TO-99) | J-Suffix (H-08) |

| OP27GJZ            | −40°C to +85°C    | 8-Lead Metal Can (TO-99) | J-Suffix (H-08) |

| OP27AZ             | −55°C to +125°C   | 8-Lead CERDIP            | Z-Suffix (Q-8)  |

| OP27AZ/883C        | −55°C to +125°C   | 8-Lead CERDIP            | Z-Suffix (Q-8)  |

| OP27EZ             | −25°C to +85°C    | 8-Lead CERDIP            | Z-Suffix (Q-8)  |

| OP27GZ             | −40°C to +85°C    | 8-Lead CERDIP            | Z-Suffix (Q-8)  |

| OP27EPZ            | 0°C to +70°C      | 8-Lead PDIP              | P-Suffix (N-8)  |

| OP27GPZ            | -40°C to +85°C    | 8-Lead PDIP              | P-Suffix (N-8)  |

| OP27GS             | -40°C to +85°C    | 8-Lead SOIC_N            | S-Suffix (R-8)  |

| OP27GS-REEL7       | −40°C to +85°C    | 8-Lead SOIC_N            | S-Suffix (R-8)  |

| OP27GSZ            | -40°C to +85°C    | 8-Lead SOIC_N            | S-Suffix (R-8)  |

| OP27GSZ-REEL       | -40°C to +85°C    | 8-Lead SOIC_N            | S-Suffix (R-8)  |

| OP27GSZ-REEL7      | −40°C to +85°C    | 8-Lead SOIC_N            | S-Suffix (R-8)  |

| OP27NBC            |                   | Die                      |                 |

$<sup>^1 \, \</sup>text{The OP27GJZ, OP27EPZ, OP27GPZ, OP27GSZ, OP27GSZ-REEL, and OP27GSZ-REEL7 are RoHS compliant parts.}$