### Features

- Bidirectional Translator of I<sup>2</sup>C Applications and SMBus Compatible

- Support Fast-mode Plus, up to 1-Mbps Data Rate

- High-Impedance SCL1, SDA1, SCL2, and SDA2 Pins for EN = LOW

- 1-V Pre-Charge on All SDA and SCL Lines Prevents Corruption during Live Board Insertion

- Operating Power Supply Range from 2.3 V to 5.5 V

- Low I<sub>CC</sub>Chip Shutdown Current: 0.3 μA (typ)

- Powered-Off High-Impedance I<sup>2</sup>C Pins

- Built-in  $\Delta V/\Delta t$  Rise Time Accelerator

- ACK Error Protection to Avoid Direction Switching Error

- ESD Protection:

- 7-kV Human-Body Model

- 1.5-kV Charged-Device Model

## Applications

- Servers/Storages

- Enterprise Switching

- Telecom Switching Equipment and Base Stations

- Industrial Automation Equipment

# Description

The TPT29511H device is a dual bidirectional  $I^2C$  and SMBus hot-swap buffer with an enable (EN) input, and works from 2.3 V to 5.5 V V<sub>CC</sub>, which supports IO cards live insertion and removal from the backplane. The control circuit prevents the backplane-side  $I^2C$  lines (in) from the other card-side  $I^2C$  lines (out) until a stop command or bus idle condition occurs on the backplane without bus contention on the card. When the connection is made, the TPT29511H provides bidirectional buffering, keeping the backplane and card capacitances isolated.

The TPT29511H rise time accelerator circuitry allows the use of weaker DC pull-up currents while also meeting rise time requirements ( $\Delta V/\Delta t > 0.6 V/us$ ).

The TPT29511H incorporates a digital enable input pin, which enables the device when asserted high and forces the device into a low current mode when asserted low, and an open-drain ready output pin, which indicates that the backplane and card sides are connected (high) or not (low).

TPT29511H is available in the MSOP8 package, and is characterized from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

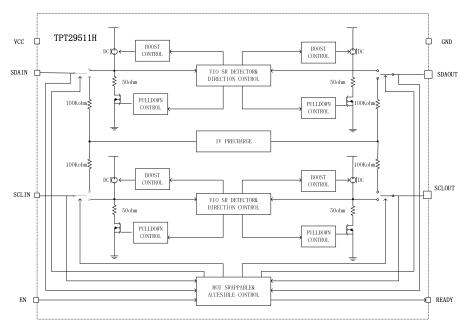

### **Functional Block Diagram**

## Hot-Swap I<sup>2</sup>C-BUS Buffer

### **Table of Contents**

| Features                                  | 1  |

|-------------------------------------------|----|

| Applications                              | 1  |

| Description                               | 1  |

| Functional Block Diagram                  | 1  |

| Revision History                          | 3  |

| Pin Configuration and Functions           | 4  |

| Specifications                            | 5  |

| Absolute Maximum Ratings <sup>(1)</sup>   | 5  |

| ESD, Electrostatic Discharge Protection   | 5  |

| Recommended Operating Conditions          | 6  |

| Thermal Information                       | 6  |

| Electrical Characteristics                | 7  |

| AC Electrical Characteristics             | 8  |

| AC Electrical Characteristics (continued) | 9  |

| Typical Performance Characteristics       | 10 |

| Test Circuitry                            | 11 |

| Test Timing Diagrams                      | 12 |

| Detailed Description                      | 13 |

| Overview                                  | 13 |

| Functional Block Diagram                  | 13 |

| Feature Description                       | 14 |

| Application and Implementation            | 15 |

| Application Information                   | 15 |

| Typical Application                       | 15 |

| Layout                                    | 16 |

| Layout Example                            | 16 |

| Tape and Reel Information                 | 17 |

| Package Outline Dimensions                | 18 |

| MSOP8                                     | 18 |

| Order Information                         | 19 |

| IMPORTANT NOTICE AND DISCLAIMER           | 20 |

## **Revision History**

| Date       | Revision | Notes            |

|------------|----------|------------------|

| 2023-12-05 | Rev.A.0  | Released version |

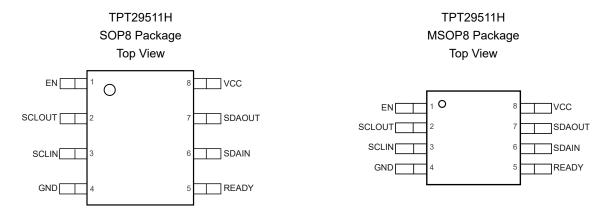

## **Pin Configuration and Functions**

#### Table 1. Pin Functions: TPT29511H

| Р   | in           | 1/0 | Description                                                                                                                                    |  |  |  |

|-----|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| No. | Name         | I/O | Description                                                                                                                                    |  |  |  |

| 1   | EN           | I   | Active-high chip enable pin. If EN is low, the device is in a low current mode.                                                                |  |  |  |

| 2   | 2 SCLOUT I/O |     | Serial clock output to and from the SCL bus on the card                                                                                        |  |  |  |

| 3   | 3 SCLIN I/O  |     | Serial clock input to and from the SCL bus on the backplane                                                                                    |  |  |  |

| 4   | GND          | -   | Ground.                                                                                                                                        |  |  |  |

| 5   | READY        | 0   | Open-drain output which pulls LOW when SDAIN and SCLIN are disconnected from SDAOUT and SCLOUT, and goes HIGH when the two sides are connected |  |  |  |

| 6   | SDAIN        | I/O | Serial data input to and from the SDA bus on the backplane                                                                                     |  |  |  |

| 7   | SDAOUT       | I/O | Serial data output to and from the SDA bus on the card                                                                                         |  |  |  |

| 8   | VCC          | -   | Power supply                                                                                                                                   |  |  |  |

## Hot-Swap I<sup>2</sup>C-BUS Buffer

## **Specifications**

### Absolute Maximum Ratings (1)

|                  | Parameter                               | Min  | Max  | Unit |

|------------------|-----------------------------------------|------|------|------|

| Vcc              | Power Supply                            | -0.5 | +7   | V    |

| IO PIN           | SDAIN, SCLIN, SDAOUT, SCLOUT, EN, READY | -0.5 | +7   | V    |

| I <sub>IK</sub>  | Input Clamp Current                     |      | -50  | mA   |

| loк              | Output Clamp Current                    |      | -50  | mA   |

| lo               | Continuous Output Current               |      | ±50  | mA   |

| Icc              | Continuous Current through VCC or GND   |      | ±100 | mA   |

| TJ               | Maximum Junction Temperature            |      | 150  | °C   |

| T <sub>STG</sub> | Storage Temperature Range               | -65  | 150  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

(2) This data was taken with the JEDEC low effective thermal conductivity test board.

(3) This data was taken with the JEDEC standard multilayer test boards.

### ESD, Electrostatic Discharge Protection

|     | Parameter                | Condition                             | Minimum Level | Unit |

|-----|--------------------------|---------------------------------------|---------------|------|

| НВМ | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1)            | 7             | kV   |

| CDM | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | 1.5           | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

|     | Parameter                  | Min                             | Max | Unit |    |

|-----|----------------------------|---------------------------------|-----|------|----|

| Vcc | Supply Voltage             |                                 | 2.3 | 5.5  | V  |

| VI  | Input Voltage Range        | EN input                        | 0   | 5.5  | V  |

| Vio | Input/output Voltage Range | SDAIN, SCLIN,<br>SDAOUT, SCLOUT | 0   | 5.5  | V  |

| Vo  | Output Voltage Range       | READY                           | 0   | 5.5  | V  |

| TA  | Ambient Temperature        |                                 | -40 | 125  | °C |

### Thermal Information

| Package Type | θյΑ | θις | Unit |

|--------------|-----|-----|------|

| MSOP8        | 205 | 44  | °C/W |

| SOP8         | 160 | 40  | °C/W |

## Hot-Swap I<sup>2</sup>C-BUS Buffer

### **Electrical Characteristics**

All test conditions: V\_{CC} = 3.3 V, T\_A = +25  $^{\circ}\text{C},$  unless otherwise noted.

|                     | Parameter                                                                                                    | Conditions                                                                                           | Min                      | Тур  | Max          | Unit |

|---------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------|------|--------------|------|

| Power Sup           | ply                                                                                                          |                                                                                                      |                          |      |              |      |

| lcc                 | Supply Current                                                                                               |                                                                                                      | 4                        | 6    | mA           |      |

| I <sub>SD</sub>     | Supply Current in Shutdown Mode through the $V_{CC}$ Pin                                                     |                                                                                                      | 0.3                      | 4    | μA           |      |

| UVLO <sup>(1)</sup> | Under Voltage Lockout (rising)                                                                               | EN = Vcc                                                                                             |                          | 2.15 |              | V    |

| UVLU                | Under Voltage Lockout (falling)                                                                              | READY = 10 k $\Omega$ to V <sub>CC</sub>                                                             |                          | 2    |              | V    |

| DC Electric         | al Characteristics                                                                                           |                                                                                                      |                          |      |              |      |

| V <sub>PRE</sub>    | Pre-charge Voltage                                                                                           | SDA, SCL = Hi-Z                                                                                      | 0.8                      | 1    | 1.2          | V    |

| I <sub>PU</sub>     | RTA pull-up Current <sup>(1)</sup>                                                                           | Position transition on SDA, SCL $V_{SDA/SCL} > 0.8 V$ , Slew rate = 1.25 $V/\mu$ s. $V_{CC}$ = 3.3 V |                          | 5    |              | mA   |

| ILI                 | Input Pin Leakage                                                                                            | SDA/SCL pins = $V_{CC}$ , or 0 V, EN = 0 V                                                           | -1                       |      | 1            | μA   |

| Vos                 | Input-output Offset Voltage<br>(SCLIN to SCLOUT, SCLOUT to<br>SCLIN and SDAIN to SDAOUT,<br>SDAOUT to SDAIN) | $R_{PU}$ for SDA/SCL = 10 k $\Omega$                                                                 | 50                       | 105  | 175          | mV   |

| I <sub>I_RDY</sub>  | Ready Pin Leakage                                                                                            | EN = V <sub>CC</sub> , READY = V <sub>CC</sub> , Bus connected                                       | -2                       |      | 2            | μA   |

| VIH                 | High-level Input Voltage                                                                                     |                                                                                                      | 0.7 ×<br>V <sub>CC</sub> |      | Vcc          | V    |

| VIL                 | Low-level Input Voltage                                                                                      | EN                                                                                                   | 0                        |      | 0.3 ×<br>Vcc | V    |

| V <sub>OL_IO</sub>  | Low-level Output Voltage                                                                                     | SDAIN, SCLIN, SDAOUT, SCLOUT, $I_{OL} = 3 \text{ mA}, V_{IN} = 0 \text{ V}$                          |                          | 0.25 | 0.4          | V    |

|                     | Low lovel Output Valtage                                                                                     | Power on, READY = L, I <sub>OL</sub> = 3 mA                                                          |                          |      | 0.4          | V    |

| Vol_ready           | Low-level Output Voltage                                                                                     | Power off, $R_{PU}$ = 10k $\Omega$ to 3.3 V                                                          |                          | 0.6  | 0.7          | V    |

| CIN(EN)             | EN input Capacitance <sup>(1)</sup>                                                                          | $V_{EN}$ = 0 V or $V_{CC}$ , f = 400 kHz                                                             |                          | 3    |              | pF   |

| CIO(READY)          | READY Output Capacitance <sup>(1)</sup>                                                                      | $V_{READY} = 0 V \text{ or } V_{CC}, f = 400 \text{ kHz}$                                            |                          | 3    |              | pF   |

| CIO(SDA/SCL)        | SDA/SCL Pin Capacitance <sup>(1)</sup>                                                                       | $V_{PIN} = 0 V \text{ or } V_{CC}, f = 400 \text{ kHz}$                                              |                          | 5    |              | pF   |

(1) Test data based on bench test and design simulation; NOT test in production.

### **AC Electrical Characteristics**

All test conditions:  $V_{CC}$  = 3.3 V,  $T_A$  = +25°C, unless otherwise noted.

|                      | Parameter                                         | Conditions                                                                                                                                        | Min                                            | Тур | Max   | Unit |  |

|----------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|-------|------|--|

| Start-up             | Switching                                         |                                                                                                                                                   |                                                |     |       |      |  |

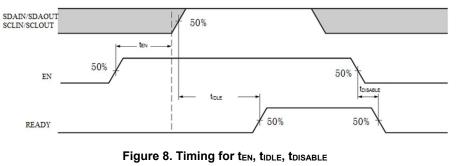

| t <sub>EN</sub>      | Time from V <sub>POR</sub> to Digital being Ready | $V_{CC}$ transition from 0 V to $V_{CC}$ ,<br>Time from $V_{POR}$ to earliest stop<br>bit recognized                                              | Time from V <sub>POR</sub> to earliest stop 50 |     |       | μs   |  |

| tIDLE                | Bus Idle Time to READY Active                     | SDA, SCL = $10 \text{ k}\Omega$ to V <sub>CC</sub><br>EN = V <sub>CC</sub><br>Measured at 0.5 × V <sub>CC</sub>                                   | 50                                             | 100 | 200   | μs   |  |

| t <sub>DISABLE</sub> | Time from EN High to Low to<br>READY Low          | SDA, SCL = $10 \text{ k}\Omega$ to V <sub>CC</sub><br>READY = $10 \text{ k}\Omega$ to V <sub>CC</sub><br>Measured at $0.5 \times V_{CC}$          |                                                | 25  | 200   | ns   |  |

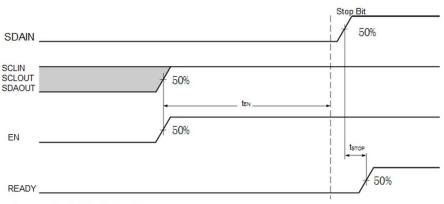

| t <sub>STOP</sub>    | SDAIN to READY Delay after<br>Stop Condition      | SDA, SCL = $10 \text{ k}\Omega$ to V <sub>CC</sub><br>READY = $10 \text{ k}\Omega$ to V <sub>CC</sub><br>Measured at $0.5 \times \text{V}_{CC}$   |                                                | 1.2 | 2     | μs   |  |

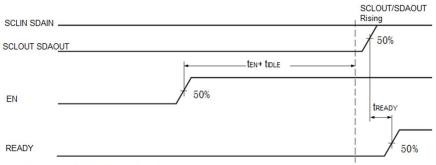

| tready               | SCLOUT/SDAOUT to READY                            | SDA, SCL = $10 \text{ k}\Omega$ to V <sub>CC</sub><br>READY = $10 \text{ k}\Omega$ to V <sub>CC</sub><br>Measured at $0.5 \times$ V <sub>CC</sub> |                                                | 1.2 | 2     | μs   |  |

| t <sub>PLH</sub>     | Low to High Propagation Delay                     | $R_{PU}$ for SDA/SCL = 10 kΩ<br>$C_L$ = 100 pF per pin<br>Measured at 0.5 × V <sub>CC</sub>                                                       |                                                | 4.5 | _ (1) | ns   |  |

| t <sub>PHL</sub>     | High to Low Propagation Delay                     | $R_{PU}$ for SDA/SCL = 10 k $\Omega$ C <sub>L</sub> =<br>100 pF per pin<br>Measured at 0.5 × V <sub>CC</sub>                                      |                                                | 66  | 150   | ns   |  |

(1) t<sub>PLH</sub> typ data based on bench test and design simulation, the max value depends on the input source and cannot test in the FT.

### **AC Electrical Characteristics (continued)**

All test conditions:  $V_{CC}$  = 3.3 V,  $T_A$  = +25°C, unless otherwise noted. <sup>(1)</sup>

|                      | Parameter                                            | Conditions             | Min           | Тур | Max | Unit |

|----------------------|------------------------------------------------------|------------------------|---------------|-----|-----|------|

| Timing cl            | haracteristics (only reference to I <sup>2</sup> C 4 | 00 kHz) <sup>(1)</sup> |               |     | 1   |      |

| f <sub>SCL_MAX</sub> | Maximum SCL Clock Frequency <sup>(1)</sup>           |                        | 400           |     |     | kHz  |

| t <sub>BUF</sub>     | Bus Free Time between a STOP and START Condition     |                        | 1.3           |     |     | μs   |

| t <sub>hd;sta</sub>  | Hold Time for a Repeated START<br>Condition          |                        | 0.6           |     |     | μs   |

| t <sub>su;sta</sub>  | Set-up Time for a Repeated START<br>Condition        |                        | 0.6           |     |     | μs   |

| tsu;sto              | Set-up Time for a STOP Condition                     |                        | 0.6           |     |     | μs   |

| t <sub>HD;DAT</sub>  | Data Hold Time                                       |                        | 0             |     |     | ns   |

| t <sub>su;dat</sub>  | Data set-up Time                                     |                        | 100           |     |     | ns   |

| t <sub>LOW</sub>     | LOW Period of the SCL Clock                          |                        | 1.3           |     |     | μs   |

| t <sub>ніGH</sub>    | HIGH Period of the SCL Clock                         |                        | 0.6           |     |     | μs   |

| t <sub>F</sub>       | Fall Time of both SDA and SCL Signals <sup>(2)</sup> |                        | 5+<br>0.1*Cb  |     | 300 | ns   |

| t <sub>R</sub>       | Rise Time of both SDA and SCL Signals <sup>(2)</sup> |                        | 20<br>+0.1*Cb |     | 300 | ns   |

(1) All timing characteristics should reference to  $I^2C$  standard @400 kHz, all parameters in table are NOT test in production.

(2)  $t_{\text{F}}$  is 6 ns on bench test, and Cb is total capacitance of one bus line in pF.

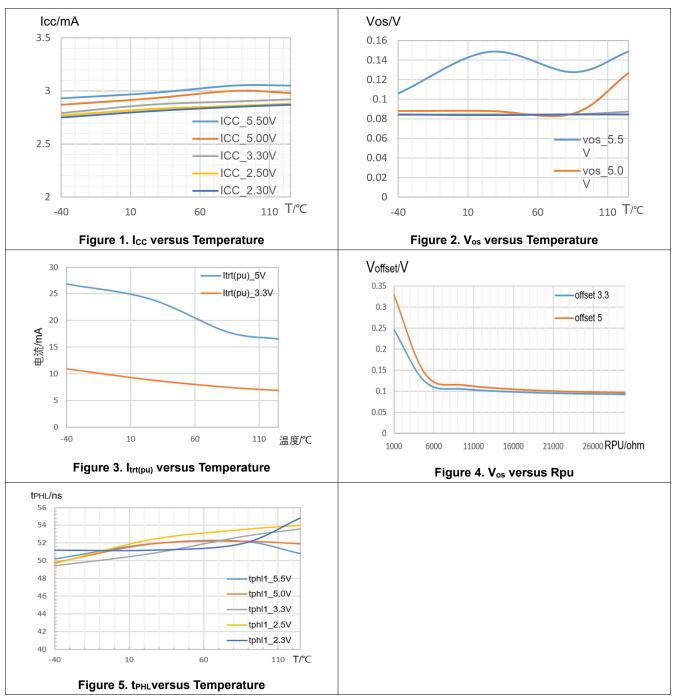

### **Typical Performance Characteristics**

All test conditions:  $V_{IN}$  =5 V,  $V_A$  =+ 25°C, unless otherwise noted.

## Hot-Swap I<sup>2</sup>C-BUS Buffer

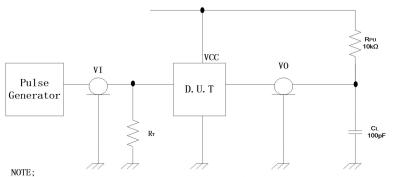

### **Test Circuitry**

Rev is pull up resistor, CL is load capacitance(includes jig and probe capacitance). Rr is terminations resistance(equal to the output impedance Zo of the pulse generators.)

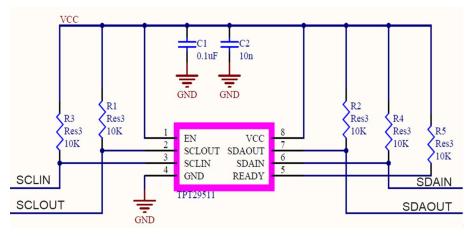

Figure 6. Test Circuitry of TPT29511H

Figure 7. Reference Circuitry of TPT29511H

### Hot-Swap I<sup>2</sup>C-BUS Buffer

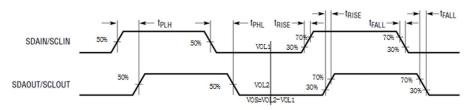

### **Test Timing Diagrams**

tstop is only aviailable after ten delay.

#### Figure 9. Timing for t<sub>STOP</sub>

tREADY is only available after tEN+tIDLE dealy.

#### Figure 10. Timing for tREADY

Figure 11. Timing for tPHL, tPLH, tR, tF, VOS

## Hot-Swap I<sup>2</sup>C-BUS Buffer

### **Detailed Description**

### Overview

The TPT29511H device is a dual bidirectional I<sup>2</sup>C and SMBus Hot-swap buffer with an enable (EN) input, and works from 2.3 V to 5.5 V V<sub>CC</sub>, which supports IO cards live insertion and removal from the backplane. The control circuit prevents the backplane-side I<sup>2</sup>C lines (in) from the other card-side I<sup>2</sup>C lines (out) until a stop command or bus idle condition occurs on the backplane without bus contention on the card. When the connection is made, the TPT29511H provides bidirectional buffering, keeping the backplane and card capacitances isolated.

The TPT29511H rise time accelerator circuitry allows the use of weaker DC pull-up currents while also meeting rise time requirements ( $\Delta V/\Delta t > 0.6 V/us$ ).

The TPT29511H incorporates a digital enable input pin, which enables the device when asserted high and forces the device into a low current mode when asserted low, and an open-drain ready output pin, which indicates that the backplane and card sides are connected (high) or not (low).

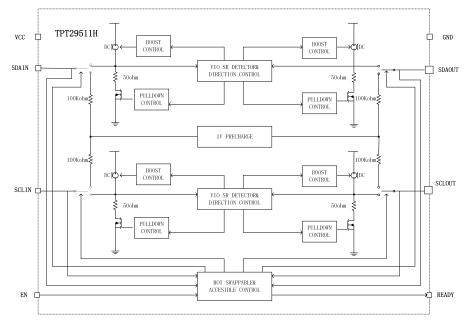

### **Functional Block Diagram**

Figure 12. Functional Block Diagram

### **Feature Description**

#### Enable (EN)

The device is in an active mode as pin EN is at high-voltage level. If EN is low, the device is in a low current mode.

#### Under-Voltage Lockout (UVLO)

The device uses an under-voltage lockout circuit to keep the device in shutdown mode until the supply voltage is higher than the UVLO threshold.

#### Over-Voltage Protection (OVP)

The device uses an over-voltage protection circuit to prevent the device from damage when the supply voltage is higher than the OVP threshold.

#### READY

The output pin will go HIGH to indicate that SDAIN and SCLIN are connected from SDAOUT and SCLOUT. And pull LOW when two sides are disconnected. The pin is driven by an open-drain pull-down capable of sinking 6 mA while holding 0.4 V on the pin. A 10-k $\Omega$  resistor is suggested connecting to VCC to provide the pull-up status.

#### **Rise Time Accelerators**

During positive bus transitions a 5-mA current source is switched on to quickly slew the SDA and SCL lines HIGH once the input level of 0.8 V for the TPT29511H is exceeded. The rising edge rate should be at least 0.6 V/µs to guarantee the accelerators turned on. The built-in  $\Delta V/\Delta t$  rise time accelerators on all SDA and SCL lines requires the bus pull-up voltage and supply voltage (VCC) to be the same. If  $\Delta V/\Delta t$  rise time accelerator < 0.2 V/µs, the time accelerators will stop to avoid the ack error.

### **Application and Implementation**

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

Note

### **Application Information**

The TPT29511H device is a dual bidirectional I<sup>2</sup>C and SMBus Hot-swap buffer, which supports IO cards live insertion and removal from backplane, such as the application in Servers/Storages and Enterprise Switching.

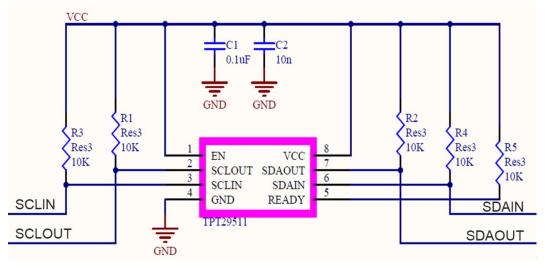

### **Typical Application**

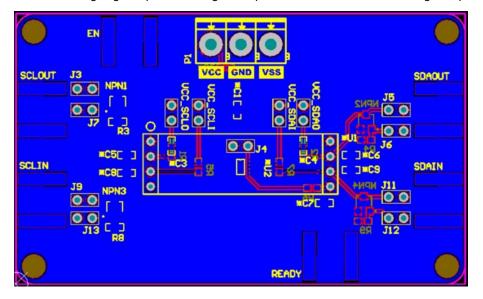

The following figures show the typical application schematics.

Figure 13. Reference Circuitry of TPT29511H

### Layout

### Layout Example

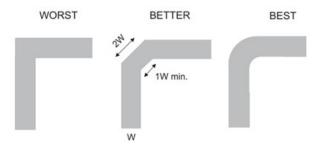

Reflections and matching are closely related to loop antenna theory, but different enough to warrant their own discussion. When a PCB trace turns a corner at a 90° angle, a reflection can occur. This is primarily due to the change in width of the trace. At the apex of the turn, the trace width is increased to 1.414 times its width. This change in width upsets the transmission line characteristics, especially the distributed capacitance and self-inductance of the trace, thus resulting in the reflection. Not all PCB traces can be straight, so they will have to turn corners. Figure 14 shows progressively better techniques of rounding corners. Only the last example (BEST) maintains constant trace width and minimizes reflections.

#### Figure 14. Trace Example

Route high-speed signals using a minimum of vias and corners which reduces signal reflections and impedance changes. When a via must be used, increase the clearance size around it to minimize its capacitance. Each via introduces discontinuities in the signal's transmission line and increases the chance of picking up interference from the other layers of the board. Be careful when designing test points, through-hole pins are not recommended at high frequencies.

## Hot-Swap I<sup>2</sup>C-BUS Buffer

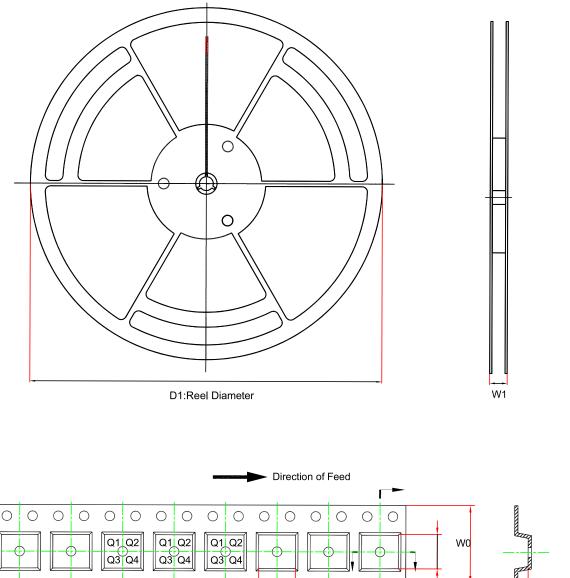

## **Tape and Reel Information**

| rder N | umber |     | Package | D' | l (mm) | W1 ( | mm) | A0 (I | mm) | B0 (mm) | К0 | (mm) | P0 (m | ım) | WO | (mm) | Pin1<br>Quadrai | nt |

|--------|-------|-----|---------|----|--------|------|-----|-------|-----|---------|----|------|-------|-----|----|------|-----------------|----|

|        |       | - 1 | I       |    |        |      |     |       |     |         |    | В0   |       |     |    |      |                 |    |

|        |       |     |         | P0 |        |      | _   |       | A   | 0       |    |      |       | _   | -  | ĸ    | 0               |    |

|        |       |     |         |    |        |      |     |       |     |         |    |      |       |     |    |      |                 |    |

| Order Number       | Package | D1 (mm) | W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P0 (mm) | W0 (mm) | Pin1<br>Quadrant |

|--------------------|---------|---------|---------|---------|---------|---------|---------|---------|------------------|

| TPT29511H-<br>VS1R | MSOP8   | 330.0   | 17.6    | 5.4     | 3.3     | 1.3     | 8.0     | 12.0    | Q1               |

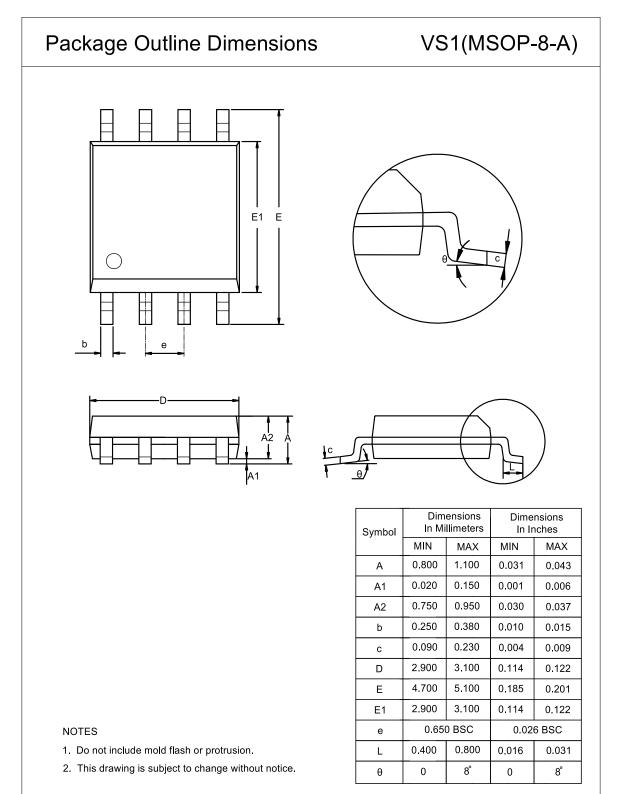

### **Package Outline Dimensions**

### MSOP8

### **Order Information**

| Order Number   | Operating Temperature<br>Range | Package | Marking Information | MSL  | Transport Media, Quantity | Eco Plan |

|----------------|--------------------------------|---------|---------------------|------|---------------------------|----------|

| TPT29511H-VS1R | −40 to 125°C                   | MSOP8   | 9511H               | MSL3 | Tape and Reel, 3000       | Green    |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2023. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.