#### **Features**

- Bidirectional Translator of 1:4 I<sup>2</sup>C Switch

- Active-Low Reset Input

- Three Address Terminals, Allowing up to Eight Devices on the I<sup>2</sup>C Bus

- Operating Power-Supply Voltage Range from 2.3 V to 5.5 V

- Allow Voltage-Level Translation among 2.5-V, 3.3-V, and 5-V Buses

- Support Standard Mode and Fast Mode I<sup>2</sup>C Devices, 0 to 400-kHz Clock Frequency

- Low Ron Switches

- · Supports Hot Insertion

- Latch-up Performance Exceeds 200 mA per JESD 78

- ESD Protection Exceeds JESD 22

- ±4000-V Human Body Model

- ±1500-V Charged Device Model

### **Applications**

- · Servers/Storages

- Routers (Telecom Switching Equipment)

- Factory Automation

- Products with I<sup>2</sup>C Slave Address Conflicts (e.g. Multiple, Identical Temp Sensors)

#### **Description**

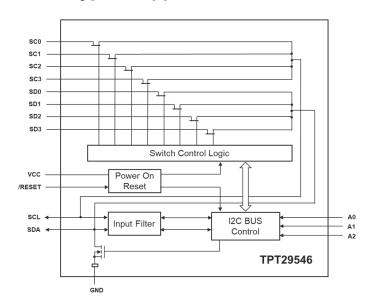

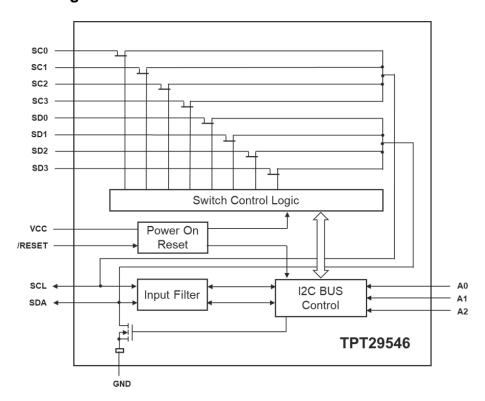

The TPT29546A is a 1:4 bidirectional translating I<sup>2</sup>C switch. The SCL/SDA upstream pair fans out to four downstream channels. Any single SCn/SDn channel or combination of channels can be selected, determined by the programmable control register.

If one of the downstream  $I^2C$  buses is stuck in a low state, then an active-low reset  $(\overline{RESET})$  input helps the TPT29546A recover. Pulling  $\overline{RESET}$  low resets the  $I^2C$  state machine and causes all the channels to be deselected, as does the internal power-on reset function.

The pass gates of the switches are constructed so that the  $V_{\text{CC}}$  terminal can be used to limit the maximum high voltage which is passed by the TPT29546A. This allows the use of different bus voltages on each pair, so that 2.5-V or 3.3-V parts can communicate with 5-V parts, without any additional protection. External pull-up resistors pull the bus up to the desired voltage level for each channel. All I/O terminals are 5.5 V tolerant.

The TPT29546A is available in the TSSOP16 and SOP16 packages, and is characterized from –40°C to +85°C.

## **Typical Application Circuit**

## **Table of Contents**

| Features                                             | 1  |

|------------------------------------------------------|----|

| Applications                                         | 1  |

| Description                                          | 1  |

| Typical Application Circuit                          | 1  |

| Revision History                                     | 3  |

| Pin Configuration and Functions                      | 4  |

| Specifications                                       | 5  |

| Absolute Maximum Ratings <sup>(1)</sup>              | 5  |

| ESD, Electrostatic Discharge Protection              | 5  |

| Recommended Operating Conditions                     | 5  |

| Thermal Information                                  | 6  |

| Electrical Characteristics-DC Parameters             | 7  |

| Electrical Characteristics-DC Parameters (Continued) | 8  |

| Electrical Characteristics-AC Parameters             | 9  |

| Switching Characteristics                            | 10 |

| Parameter Measurement Waveforms                      | 11 |

| Detailed Description                                 | 12 |

| Overview                                             | 12 |

| Functional Block Diagram                             | 12 |

| Application and Implementation                       | 13 |

| Application Information                              | 13 |

| Tape and Reel Information                            | 15 |

| Package Outline Dimensions                           | 16 |

| TSSOP16                                              | 16 |

| SOP16                                                | 17 |

| Order Information                                    | 18 |

| IMPORTANT NOTICE AND DISCLAIMER                      | 10 |

# **Revision History**

| Date       | Revision | Notes                                             |  |  |  |

|------------|----------|---------------------------------------------------|--|--|--|

| 2022-12-06 | Rev.A.0  | Initial version.                                  |  |  |  |

| 2024-09-23 | Rev.A.1  | Updated to new datasheet format.                  |  |  |  |

| 2024-09-23 |          | Added the hot insertion function in the Features. |  |  |  |

www.3peak.com 3 / 20 CA20240805A1

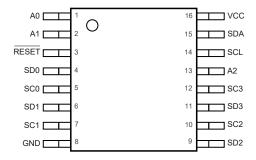

# **Pin Configuration and Functions**

TPT29546A SOP16/TSSOP16 Top View

Table 1. Pin Functions: TPT29546A

| Pin No. | Name  | I/O    | Description                                                                                |

|---------|-------|--------|--------------------------------------------------------------------------------------------|

| 1       | A0    | I      | Address input 0. Connect directly to V <sub>CC</sub> or GND.                               |

| 2       | A1    | I      | Address input 1. Connect directly to V <sub>CC</sub> or GND.                               |

| 3       | RESET | I      | Active-low reset input. Connect to V <sub>CC</sub> through a pull-up resistor if not used. |

| 4       | SD0   | I/O    | Serial data 0. Connect to the power of slave channel 0 through a pull-up resistor.         |

| 5       | SC0   | I/O    | Serial clock 0. Connect to the power of slave channel 0 through a pull-up resistor.        |

| 6       | SD1   | I/O    | Serial data 1. Connect to the power of slave channel 1 through a pull-up resistor.         |

| 7       | SC1   | I/O    | Serial clock 1. Connect to the power of slave channel 1 through a pull-up resistor.        |

| 8       | GND   | GND    | Ground.                                                                                    |

| 9       | SD2   | I/O    | Serial data 2. Connect to the power of slave channel 0 through a pull-up resistor.         |

| 10      | SC2   | I/O    | Serial clock 2. Connect to the power of slave channel 0 through a pull-up resistor.        |

| 11      | SD3   | I/O    | Serial data 3. Connect to the power of slave channel 0 through a pull-up resistor.         |

| 12      | SC3   | I/O    | Serial clock 3. Connect to the power of slave channel 0 through a pull-up resistor.        |

| 13      | A2    | I      | Address input 2. Connect directly to V <sub>CC</sub> or GND.                               |

| 14      | SCL   | I/O    | Clock bus. Connect to V <sub>CC</sub> through a pull-up resistor.                          |

| 15      | SDA   | I/O    | Data bus. Connect to V <sub>CC</sub> through a pull-up resistor.                           |

| 16      | Vcc   | Supply | Supply power.                                                                              |

www.3peak.com 4 / 20 CA20240805A1

## **Specifications**

### Absolute Maximum Ratings (1)

|                  | Parameter                      | Condition          | Min  | Max  | Unit |

|------------------|--------------------------------|--------------------|------|------|------|

| Vcc              | Supply Voltage                 |                    | -0.5 | 7    | V    |

| Vı               | Input Voltage                  |                    | -0.5 | 7    | V    |

| I <sub>IK</sub>  | Input Clamp Current            | V <sub>1</sub> < 0 |      | ±20  | mA   |

| lok              | Output Clamp Current           | V <sub>0</sub> < 0 |      | ±25  | mA   |

| Icc              | Continuous Current through GND |                    |      | ±100 | mA   |

| TJ               | Maximum Junction Temperature   |                    |      | 125  | °C   |

| T <sub>A</sub>   | Operating Temperature Range    |                    | -45  | 85   | °C   |

| T <sub>STG</sub> | Storage Temperature            |                    | -60  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                  | Minimum Level | Unit |

|--------|--------------------------|----------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | ±4            | kV   |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | ±1.5          | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### **Recommended Operating Conditions**

| Parameter       |                             | Condition     | Min                      | Max                      | Unit |

|-----------------|-----------------------------|---------------|--------------------------|--------------------------|------|

| Vcc             | Supply Voltage              |               | 2.3                      | 5.5                      | V    |

| VIH             | High-Level Input Voltage    | SCL, SDA      | 0.7 ×<br>V <sub>CC</sub> | 5.5                      | V    |

|                 |                             | A1, A0, RESET | 0.7 ×<br>V <sub>CC</sub> | 5.5                      | V    |

| V <sub>IL</sub> | Low-Level Input Voltage     | SCL, SDA      | -0.5                     | 0.3 ×<br>V <sub>CC</sub> | mA   |

|                 |                             | A1, A0, RESET | -0.5                     | 0.3 ×<br>Vcc             | mA   |

| TA              | Operating Temperature Range |               | -40                      | 85                       | °C   |

www.3peak.com 5 / 20 CA20240805A1

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **Thermal Information**

| Package Type | θ <sub>JA</sub> | θυς | Unit |

|--------------|-----------------|-----|------|

| TSSOP16      | 125             | 61  | °C/W |

| SOP16        | 97              | 55  | °C/W |

www.3peak.com 6 / 20 CA20240805A1

#### **Electrical Characteristics-DC Parameters**

All test conditions:  $V_{CC}$  = 2.3 V to 3.6 V,  $T_A$  = -40 to +85°C, unless otherwise noted.

| Symbol             | Parameter                                         | Conditions                                                                                 | Min                 | Тур | Max                 | Unit |

|--------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------|-----|---------------------|------|

| Supply             |                                                   |                                                                                            |                     |     |                     |      |

| l                  | Supply Current in Operating                       | $V_{CC}$ = 3.6 V; no load; $V_{I}$ = $V_{CC}$ or GND;<br>ing $f_{SCL}$ = 100 kHz           |                     | 2.4 | 20                  | μΑ   |

| I <sub>DD</sub>    | Mode                                              | $V_{CC}$ = 3.6 V; no load; $V_I$ = $V_{CC}$ or GND; $f_{SCL}$ = 400 kHz                    | -                   | 6.5 | 30                  | μΑ   |

| I <sub>STB</sub>   | Standby Current                                   | V <sub>CC</sub> = 3.6 V; no load; V <sub>I</sub> = V <sub>CC</sub> or GND                  | -                   | 0.9 | 3.0                 | μΑ   |

| V                  | Power-on Reset Voltage, V <sub>CC</sub><br>Rising | No loads V = V = ar CND                                                                    | -                   | 1.2 | 1.45                | V    |

| $V_{POR}$          | Power-on Reset Voltage, Vcc<br>Falling            | No load; V <sub>I</sub> = V <sub>CC</sub> or GND                                           | 0.8                 | 1.2 |                     | ٧    |

| Input SC           | Lx; Input/Output SDAx                             |                                                                                            |                     |     |                     |      |

| VIL                | Low-Level Input Voltage                           | V <sub>CC</sub> = 2.3 V                                                                    |                     |     | 0.3 V <sub>CC</sub> | V    |

| V <sub>IH</sub>    | High-Level Input Voltage                          | V <sub>CC</sub> = 2.3 V                                                                    | 0.7 Vcc             |     |                     | ٧    |

|                    | Lave Lavel Output Commant                         | $V_{CC} = 2.3 \text{ V}, V_{OL} = 0.4 \text{ V}$                                           | 3                   | 10  |                     | mA   |

| l <sub>OL</sub>    | Low-Level Output Current                          | $V_{CC} = 2.3 \text{ V}, V_{OL} = 0.6 \text{ V}$                                           | 6                   | 13  |                     | mA   |

| IL                 | Leakage Current                                   | $V_{CC} = 2.3 \text{ V}, V_I = V_{CC} \text{ or GND}$                                      | -1                  | 0.1 | 1                   | μΑ   |

| Cı                 | Input Capacitance (1)                             | V <sub>I</sub> = GND                                                                       |                     | 15  |                     | pF   |

| Select In          | puts A0, A1, RESET                                |                                                                                            |                     |     |                     |      |

| VIL                | Low-Level Input Voltage                           | V <sub>CC</sub> = 2.3 V                                                                    |                     |     | 0.3 Vcc             | ٧    |

| $V_{IH}$           | High-Level Input Voltage                          | V <sub>CC</sub> = 2.3 V                                                                    | 0.7 V <sub>CC</sub> |     |                     | ٧    |

| ILI                | Input Leakage Current                             | V <sub>CC</sub> = 2.3 V, pin at V <sub>CC</sub> or GND                                     | -1                  | 0.1 | 1                   | μA   |

| Cı                 | Input Capacitance <sup>(1)</sup>                  | V <sub>I</sub> = GND                                                                       |                     | 3   |                     | pF   |

| Pass Gat           | е                                                 |                                                                                            |                     |     |                     |      |

| В                  | On-State Resistance                               | $V_{CC}$ = 3.0 V to 3.6 V; $V_{O}$ = 0.4 V; $I_{O}$ = 15 mA                                | 0                   | 4.8 | 25                  | Ω    |

| R <sub>ON</sub>    | On-State Resistance                               | Vcc = 2.3 V to 2.7 V; Vo = 0.4 V;<br>Io = 10 mA                                            | 0                   | 6.5 | 30                  | Ω    |

| V <sub>O(SW)</sub> | Switch Output Voltage (1)                         | $V_{I(SW)} = V_{CC} = 3.0 \text{ V to } 3.6 \text{ V};$<br>$I_{O(SW)} = -100  \mu\text{A}$ | 1.6                 | 2.1 | 2.8                 | V    |

|                    |                                                   | $V_{I(SW)} = V_{CC} = 2.3 \text{ V to } 2.7 \text{ V};$<br>$I_{O(SW)} = -100  \mu\text{A}$ | 1.0                 | 1.5 | 2.0                 | V    |

| IL                 | Leakage Current                                   | V <sub>I</sub> = V <sub>CC</sub> or GND                                                    | -1                  | 0.1 | 1                   | μA   |

| C <sub>IO</sub>    | Input/Output Capacitance (1)                      | V <sub>I</sub> = GND                                                                       |                     | 3   |                     | pF   |

<sup>(1)</sup> Parameters are provided by lab bench tests and design simulation. Not tested in production.

www.3peak.com 7 / 20 CA20240805A1

## **Electrical Characteristics-DC Parameters (Continued)**

All test conditions:  $V_{CC}$  = 4.5 V to 5.5 V,  $T_A$  = -40 to +85°C, unless otherwise noted.

| Symbol             | Parameter                         | Conditions                                                                                      | Min                 | Тур  | Max                 | Unit |

|--------------------|-----------------------------------|-------------------------------------------------------------------------------------------------|---------------------|------|---------------------|------|

| Supply             |                                   |                                                                                                 |                     |      |                     |      |

| ı                  | Supply Current in Operating       | $V_{CC}$ = 5.5 V; no load; $V_I$ = $V_{CC}$ or GND; $f_{SCL}$ = 100 kHz                         | -                   | 5    | 20                  | μΑ   |

| I <sub>DD</sub>    | Mode                              | $V_{CC}$ = 5.5 V; no load; $V_I$ = $V_{CC}$ or GND; $f_{SCL}$ = 400 kHz                         |                     | 14   | 30                  | μΑ   |

| I <sub>STB</sub>   | Standby Current                   | $V_{CC}$ = 5.5 V; no load; $V_I$ = $V_{CC}$ or GND                                              | -                   | 1.8  | 3.0                 | μA   |

|                    | Power-on Reset Voltage<br>Rising  | Na laada W. W. as OND                                                                           | -                   | 1.25 | 1.45                | V    |

| V <sub>POR</sub>   | Power-on Reset Voltage<br>Falling | No load; V <sub>I</sub> = V <sub>CC</sub> or GND                                                | 0.8                 | 1.2  |                     | V    |

| Input SC           | L; Input/Output SDA               |                                                                                                 | ·                   |      |                     |      |

| V <sub>IL</sub>    | Low-Level Input Voltage (1)       | V <sub>CC</sub> = 5.5 V                                                                         |                     |      | 0.3 V <sub>CC</sub> | V    |

| VIH                | High-Level Input Voltage          | V <sub>CC</sub> = 5.5 V                                                                         | 0.7 Vcc             |      |                     | V    |

|                    | Low-Level Output Current          | $V_{CC} = 5.5 \text{ V}, V_{OL} = 0.4 \text{ V}$                                                | 3                   | 22   |                     | mA   |

| I <sub>OL</sub>    |                                   | $V_{CC} = 5.5 \text{ V}, V_{OL} = 0.6 \text{ V}$                                                | 6                   | 32   |                     | mA   |

| IL                 | Leakage Current                   | V <sub>I</sub> = V <sub>CC</sub> or GND                                                         | -1                  | 0.1  | 1                   | μA   |

| Cı                 | Input Capacitance (1)             | V <sub>I</sub> = GND                                                                            |                     | 15   |                     | pF   |

| Select In          | puts A0 to A2, RESET              |                                                                                                 |                     |      |                     |      |

| VIL                | Low-Level Input Voltage           | V <sub>CC</sub> = 5.5 V                                                                         |                     |      | 0.3 Vcc             | ٧    |

| $V_{IH}$           | High-Level Input Voltage          | V <sub>CC</sub> = 5.5 V                                                                         | 0.7 V <sub>CC</sub> |      |                     | V    |

| ILI                | Input Leakage Current             | Pin at V <sub>CC</sub> or GND                                                                   | -1                  | 0.1  | 1                   | μΑ   |

| Cı                 | Input Capacitance (1)             | V <sub>I</sub> = GND                                                                            |                     | 3    |                     | pF   |

| Pass Gat           | е                                 |                                                                                                 |                     |      |                     |      |

| R <sub>ON</sub>    | On-State Resistance               | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V};$<br>$V_{O} = 0.4 \text{ V};$ $I_{O} = 15 \text{ mA}$ | 1                   | 3.3  | 20                  | Ω    |

| V <sub>O(SW)</sub> | Switch Output Voltage (1)         | $V_{I(SW)} = V_{CC} = 4.5 \text{ V to } 5.5 \text{ V};$<br>$I_{O(SW)} = -100  \mu\text{A}$      | 2.6                 | 3.55 | 4.5                 | V    |

| IL                 | Leakage Current                   | V <sub>I</sub> = V <sub>CC</sub> or GND                                                         | -1                  | 0.1  | 1                   | μA   |

| C <sub>IO</sub>    | Input/Output Capacitance (1)      | V <sub>I</sub> = GND                                                                            |                     | 3    |                     | pF   |

<sup>(1)</sup> Parameters are provided by lab bench tests and design simulation. Not tested in production.

www.3peak.com 8 / 20 CA20240805A1

#### **Electrical Characteristics-AC Parameters**

#### I<sup>2</sup>C Interface Timing Requirements

All test conditions: over recommended operating free-air temperature range, unless otherwise noted.

|                       | Parameter                                                         | Condition                                | Min        | Max | Unit |

|-----------------------|-------------------------------------------------------------------|------------------------------------------|------------|-----|------|

| I <sup>2</sup> C Bus— | Fast Mode                                                         |                                          |            |     |      |

| f <sub>SCL</sub>      | I <sup>2</sup> C Clock Frequency                                  |                                          | 0          | 400 | kHz  |

| t <sub>SCH</sub>      | I <sup>2</sup> C Clock High Time                                  |                                          | 0.6        |     | μs   |

| t <sub>SCL</sub>      | I <sup>2</sup> C Clock Low Time                                   |                                          | 1.3        |     | μs   |

| t <sub>SP</sub>       | I <sup>2</sup> C Spike Time                                       |                                          |            | 50  | ns   |

| t <sub>SDS</sub>      | I <sup>2</sup> C Serial Data Setup Time                           |                                          | 100        |     | ns   |

| t <sub>SDH</sub>      | I <sup>2</sup> C Serial Data Hold Time                            |                                          | 0          |     | ns   |

| t <sub>ICR</sub>      | I <sup>2</sup> C Input Rise Time                                  |                                          | 20         | 300 | ns   |

| t <sub>ICF</sub>      | I <sup>2</sup> C Input Fall Time                                  |                                          | 20 + 0.1Cb | 300 | ns   |

| tocf                  | I <sup>2</sup> C Output Fall Time (1)                             | 10-pF to 400-pF bus                      | 20 + 0.1Cb | 300 | ns   |

| t <sub>BUF</sub>      | I <sup>2</sup> C Bus Free Time between<br>Stop and Start          |                                          | 1.3        |     | μs   |

| t <sub>STS</sub>      | I <sup>2</sup> C Start or Repeated Start<br>Condition Setup       |                                          | 0.6        |     | μs   |

| t <sub>sтн</sub>      | I <sup>2</sup> C Start or Repeated Start<br>Condition Hold        |                                          | 0.6        |     | μs   |

| t <sub>SPS</sub>      | I <sup>2</sup> C Stop Condition Setup                             |                                          | 0.6        |     | μs   |

| t <sub>VD(Data)</sub> | Valid Data Time                                                   | SCL low to SDA output valid              |            | 0.9 | μs   |

| t <sub>VD(ACK)</sub>  | Valid Data Time of ACK<br>Condition                               | ACK signal from SCL low to SDA (out) low |            | 0.9 | μs   |

| t <sub>SP</sub>       | Pulse Width of Spikes that must be Suppressed by the Input Filter |                                          |            | 50  | ns   |

| t <sub>PD</sub>       | Propagation Delay <sup>(1)</sup>                                  | From SDA to SDx, or SCL to SCx           |            | 0.3 | ns   |

| Св                    | I <sup>2</sup> C Bus Capacitive Load                              |                                          |            | 400 | pF   |

<sup>(1)</sup> The propagation delay is calculated from the 20 typical  $R_{\text{ON}}$  and the 15-pF load capacitance.

www.3peak.com 9 / 20 CA20240805A1

<sup>(2)</sup> The above parameters are provided by lab bench tests and design simulation. Not tested in production.

## **Switching Characteristics**

All test conditions: over recommended operating free-air temperature range,  $C_L \le 100$  pF, unless otherwise noted.

| Symbol               | Description                         | Condition   | Min | Max  | Unit |

|----------------------|-------------------------------------|-------------|-----|------|------|

| _                    | Data Valid Time                     | High to Low |     | 1    | μs   |

| T <sub>VD; DAT</sub> | Data Valid Time                     | Low to High |     | 0.55 | μs   |

| T <sub>VD; DAT</sub> | Data Valid Time<br>Acknowledge Time |             |     | 1    | ns   |

| RESET                |                                     |             |     |      |      |

| t <sub>W(RST)L</sub> | Low-Level Reset Time                |             | 4   |      | ns   |

| t <sub>RST</sub>     | Reset Time                          | SDA clear   |     | 500  | ns   |

| t <sub>REC;STA</sub> | Recovery Time to START Condition    |             | 0   |      | ns   |

<sup>(1)</sup> Parameters are provided by lab bench tests and design simulation. Not tested in production.

www.3peak.com 10 / 20 CA20240805A1

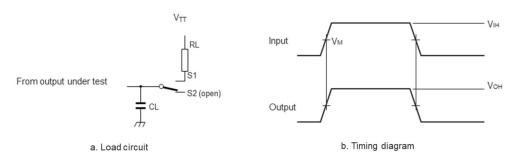

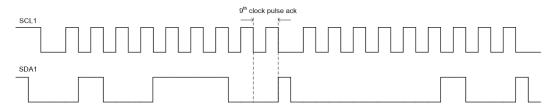

#### **Parameter Measurement Waveforms**

Figure 1. Load Circuit for Outputs

www.3peak.com 11 / 20 CA20240805A1

## **Detailed Description**

#### **Overview**

The TPT29546A is a 1:4 bidirectional translating  $I^2C$  switch. The SCL/SDA upstream pair fans out to four downstream channels. Any single SCn/SDn channel or combination of channels can be selected, determined by the programmable control register.

If one of the downstream  $I^2C$  buses is stuck in a low state, then an active-low reset ( $\overline{RESET}$ ) input helps the TPT29546A recover. Pulling  $\overline{RESET}$  low resets the  $I^2C$  state machine and causes all the channels to be deselected, as does the internal power-on reset function.

#### **Functional Block Diagram**

Figure 2. Functional Block Diagram

www.3peak.com 12 / 20 CA20240805A1

## **Application and Implementation**

#### Note

Information in the following application sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### **Application Information**

Figure 3. I<sup>2</sup>C Bus (2.3 V~5.5 V) Waveform

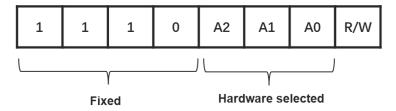

#### **Device Address**

Following a START condition, the bus master must output the address of the slave when it is accessing. To conserve power, no internal pull-up resistor is incorporated on the hardware selectable address pins, and they must be pulled High or Low. The address of the TPT29546A is shown below.

Figure 4. Slave Device Address

#### **Control Register**

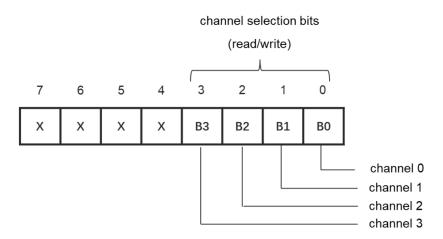

Following the successful acknowledgment of the slave address, the bus master sends a byte to the TPT29546A, which is stored in the control register. If multiple bytes are received by the TPT29546A, it saves the last byte received. This register can be written and read via the  $I^2C$  bus.

www.3peak.com 13 / 20 CA20240805A1

Figure 5. Control Register

#### **Control Register Definition**

One or several SCx/SDx downstream pairs, or channels, are selected by the contents of the control register. This register is written after the TPT29546A. The 4 LSBs of the control byte determines which channel is to be selected. When a channel is selected, the channel becomes active after a STOP condition has been placed on the I<sup>2</sup>C bus. This ensures that all SCx/SDx lines are in a high state when the channel is active so that no false conditions occur during the connection.

Table 2. Control Register: Write—Channel Selection; Read—Channel Status

| В7 | В6 | B5 | B4 | В3 | B2 | B1 | В0 | Command                |

|----|----|----|----|----|----|----|----|------------------------|

| х  | х  | х  | х  | x  | x  | х  | 0  | Channel 0 disable      |

| х  | х  | х  | х  | х  | х  | х  | 1  | Channel 0 enable       |

| х  | х  | х  | х  | х  | х  | 0  | х  | Channel 1 disable      |

| х  | х  | х  | х  | х  | х  | 1  | х  | Channel 1 enable       |

| х  | х  | х  | х  | х  | 0  | х  | х  | Channel 2 disable      |

| х  | х  | х  | х  | х  | 1  | х  | х  | Channel 2 enable       |

| х  | х  | х  | х  | 0  | х  | х  | х  | Channel 3 disable      |

| х  | х  | х  | х  | 1  | х  | х  | х  | Channel 3 enable       |

|    |    |    |    |    |    |    |    | No channel selected;   |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | power-up/reset default |

|    |    |    |    |    |    |    |    | state                  |

<sup>(1)</sup> Multiple channels can be enabled at the same time. Example: B3 = 0, B2 = 1, B1 = 1, B0 = 0, which means that channel 0 and channel 3 are disabled while channel 1 and channel 2 are enabled. Care should be taken not to exceed the maximum bus capacitance.

www.3peak.com 14 / 20 CA20240805A1

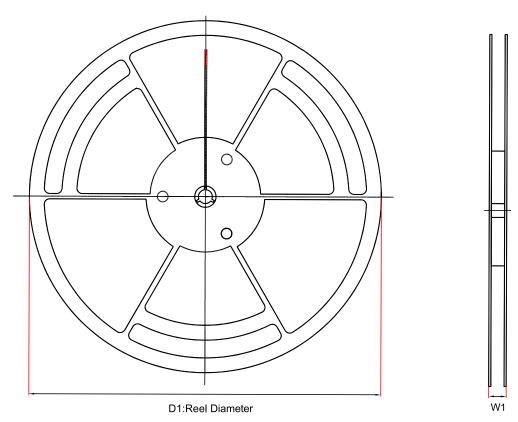

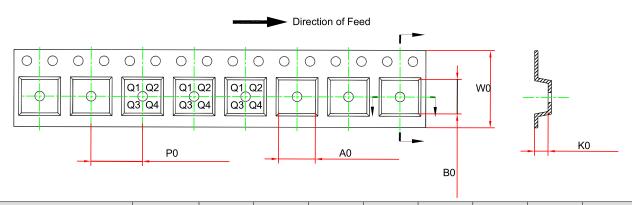

# **Tape and Reel Information**

| Order Number   | Package | D1<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadrant |

|----------------|---------|------------|------------|------------|------------|------------|------------|------------|------------------|

| TPT29546A-TS3R | TSSOP16 | 330        | 6.8        | 1.3        | 12         | 17.6       | 5.4        | 8          | Q1               |

| TPT29546A-SO3R | SOP16   | 330        | 6.7        | 2.1        | 16         | 21.6       | 10.4       | 8          | Q1               |

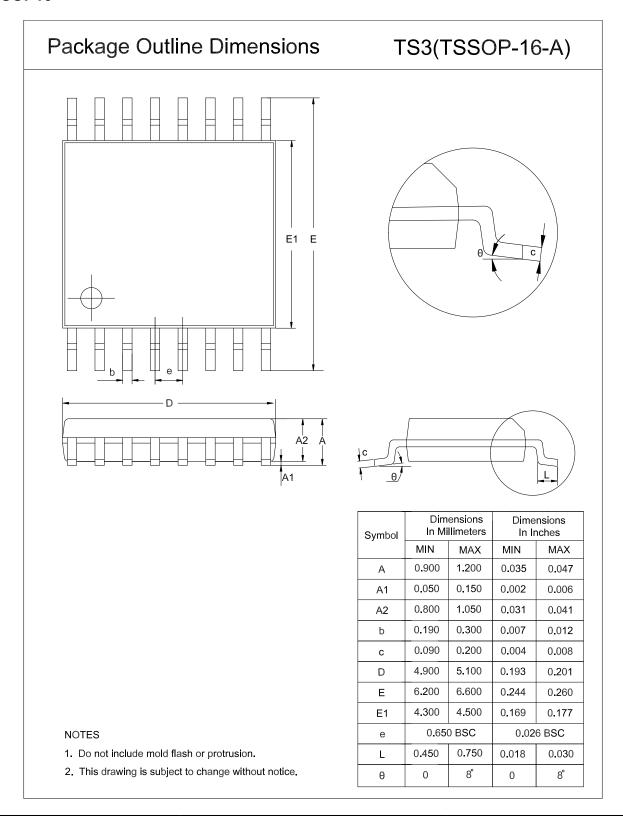

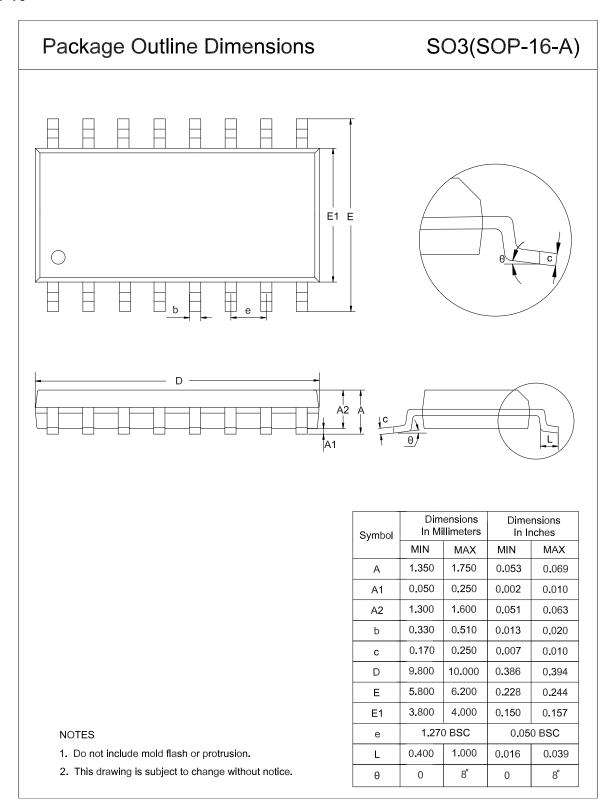

## **Package Outline Dimensions**

#### TSSOP16

#### SOP16

### **Order Information**

| Order Number       | Operating Temperature<br>Range | Package | Marking Information | MSL | Transport Media, Quantity | Eco Plan |

|--------------------|--------------------------------|---------|---------------------|-----|---------------------------|----------|

| TPT29546A-TS3R     | −40 to 85°C                    | TSSOP16 | 9546A               | 3   | Tape and Reel, 3,000      | Green    |

| TPT29546A-SO3R (1) | −40 to 85°C                    | SOP16   | 9546A               | 3   | Tape and Reel, 2,500      | Green    |

<sup>(1)</sup> For future products, contact the 3PEAK factory for more information and samples.

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 18 / 20 CA20240805A1

#### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2024. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 19 / 20 CA20240805A1

This page intentionally left blank