# NMOS NINPUT/OUTPUT **EXPANDER**

MB 88304 MB 88305

April 1986 Edition 1.1

#### NMOS INPUT/OUTPUT EXPANDER

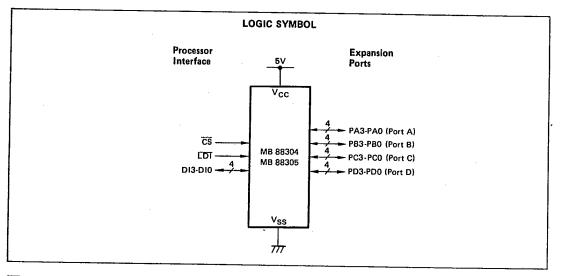

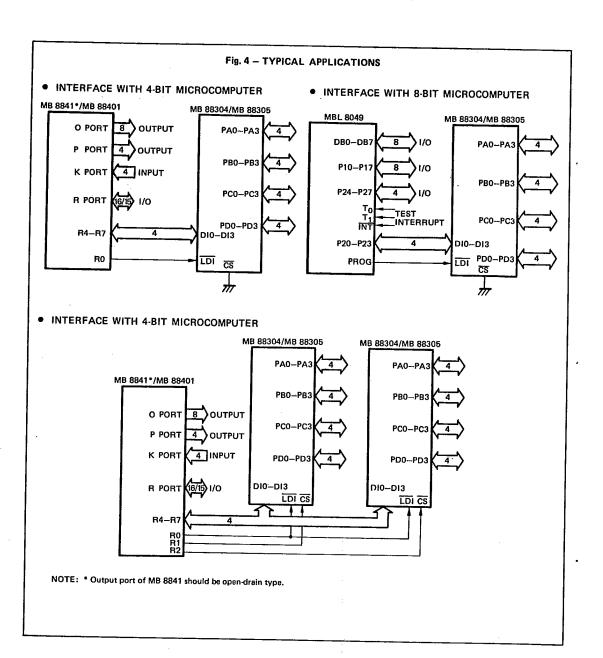

The Fujitsu MB 88304/MB 88305 are peripheral integrated circuits that can be connected to a 4-bit or 8-bit single-chip microcomputer (MCU) to provide additional I/O ports. Besides furnishing simple I/O port expansion, the MB 88304 and MB 88305 can AND or OR port data with data from the MCU, on instruction from the MCU.

The MB 88304/MB 88305 are pseudo-bidirectional ports. They are accessed in 4-bit units, but each individual bit can be used for either input or output, and input and output can be intermixed. The interface to the MCU requires only the connection of a 4-bit interface port and a strobe signal. All output ports of the MB 88304 are open-drain; MB 88305 output ports all have pull-up resistors. The output ports on both chips are reset to the high-impedance state

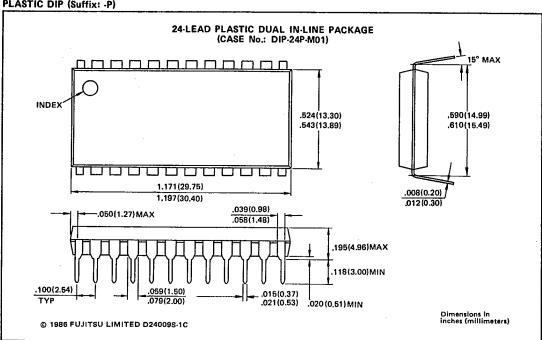

The MB 88304/MB 88305 are fabricated with N-channel silicon-gate E/D MOS process, and packaged in 24-pin plastic DIP. Also, they are powered with a single +5V power supply, and operate over the ambient temperature range of -30°C to +70°C.

#### **FEATURES**

- Four 4-bit I/O ports (16 lines)

- Four Functions: parallel input, parallel output, AND output, and OR output

- AND and OR functions provide individual output capability

- Single-bit input/output: Input and output can be intermixed on each port

- High output drive

- Built-in power-on reset circuit

- CS pin for simplified input/output expansion

- Two output circuit types: Open-drain output (MB 88304) 3-state output (MB 88305)

- Easily connectable to MCUs with 8243 interface

- Single +5V power supply

- -30°C to +70°C operating temperature range

- N-channel silicon-gate E/D MOS process

- 24-pin plastic DIP (Suffix: -P)

| PB0•□1         | 24 Vcc  |

|----------------|---------|

| PA0* 2         | 23 PB1  |

| · ¬            |         |

| PA1*□3         | 22 PB2* |

| PA2*□4         | 21 PB3* |

| PA3*□5         | 20 PC0* |

|                | 19 PC1* |

| CDI 7 TOP VIEW | 18 PC2* |

| D13 🗆 8        | 17 PC3* |

| DI2 🗖 9        | 16 PD3* |

| DI1 🗆 10       | 15 PD2* |

| DI0 🗆 11       | 14 PD1* |

| GND ☐ 12       | 13 PD0* |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance

FUJITSU

FUJITSU MB 88304 MB 88305

MB 88304 FUJITSU MB 88305

T-52-33-03

## PIN DESCRIPTION

The MB 88304/88305 have two interfaces: One is the processor interface;  $\overline{CS}$ ,  $\overline{LDI}$ , and DI3-DI0, which are used for the processor to communicate with the MB 88304/5 devices. Another is the expansion I/O ports; Ports A, B, C, and D, which serve as an expansion of the processor's I/O.

PIN DESCRIPTION

| Table 1 - PIN C     | DESCRIPTION    |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|----------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol              | Pin No.        | Туре                                                                                                 | Name/Function                                                                                                                                                                                                                                                                                                                                                                                  |

| Vcc                 | 24             | _                                                                                                    | V <sub>CC</sub> : is the +5V power supply pin.                                                                                                                                                                                                                                                                                                                                                 |

| GND                 | 12             | _                                                                                                    | GND: is the ground pin.                                                                                                                                                                                                                                                                                                                                                                        |

| <del>CS</del>       | 6              | ı                                                                                                    | Chip Select: is a low-level-sense high-impedance input. A low level on this input selects the device. This input is TTL-compatible.                                                                                                                                                                                                                                                            |

| <u>LDI</u>          | 7              | ı                                                                                                    | Load Data Input: is an edge-triggered strobe input. The operation code and address code on DIO to DI3 are latched at the LDI falling edge. The data transffered via DIO to DI3 becomes valid on the rising edge of the LDI input.                                                                                                                                                              |

| DI3 to DI0          | 8 to 11        | 1/0                                                                                                  | Data Bus: is a 4-bit bidirectional port used for interface to the MCU. The operation code and address code provided by the MCU on this port are latched at the falling edge of the LDI strobe input, and input/output data is transferred at the rising edge of the LDI. The DI port remains in the high-impedance state except when the input operation is executed.                          |

| PA0 to PA3          | 2 to 5         | 1/0                                                                                                  | Ports A, B, C, and D are 4-bit bidirectional ports used as expansion I/O ports.  These four ports are addressed by address codes provided by the MCU.                                                                                                                                                                                                                                          |

| PB0,<br>PB1 to PB3  | 1,<br>21 to 23 | 1/0                                                                                                  | When an input operation code is given by the MCU, data on the addressed port is transferred to the DI0 to DI3 at the rising edge of the LDI. When an output operation code is provided, data on the DI0 to DI3 is transferred and latched to the addressed port at the rising edge of the LDI. Logical operations are also possible, in which data on the addressed port is ANDed or ORed with |

| PC0 to PC3 20 to 17 | 1/0            | data on the DIO to DI3 and the result is latched at the addressed port at the rising edge of the DI. |                                                                                                                                                                                                                                                                                                                                                                                                |

| PD0 to PD3          | 16 to 13       | 1/0                                                                                                  | After a power-on reset, Ports A to D are all set to the high-impedance state.  An individual port is released from the high-impedance state when the OUT,  AND, or OR function is applied to it. (Since the MB 88304 has open-drain outputs, a line returns to the high-impedance state when an "1" is written on it.)                                                                         |

MB 88304 MB 88305

## FUNCTIONAL DESCRIPTION

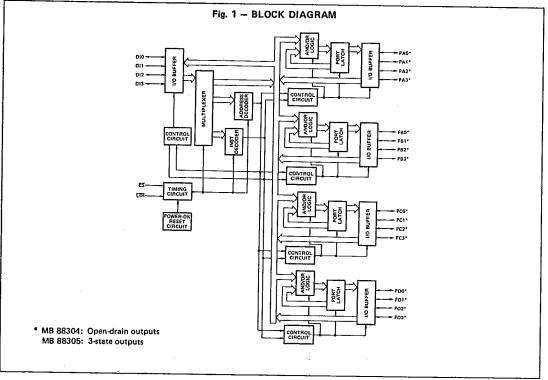

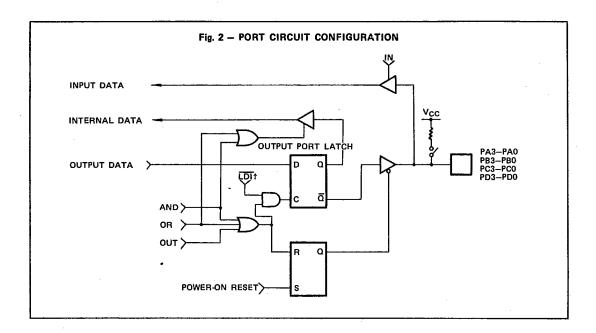

The four 4-bit I/O ports of the MB 88304 and MB 88305 are labelled port A, port B, port C, and port D (PA, PB, PC, and PD). They serve as expansion I/O ports for a one-chip microcomputer (MCU), and can be accessed via an MCU port. Their functions are as follows:

- Data transfer from the MCU to port A, B, C, or D

- Data transfer from port A, B, C, or D to the MCU

- ANDing of the port A, B, C, or D data with MCU data and latching of the result at port A, B, C, or D

- ORing of the port A, B, C, or D data with MCU data and latching of the result at port A, B, C, or D

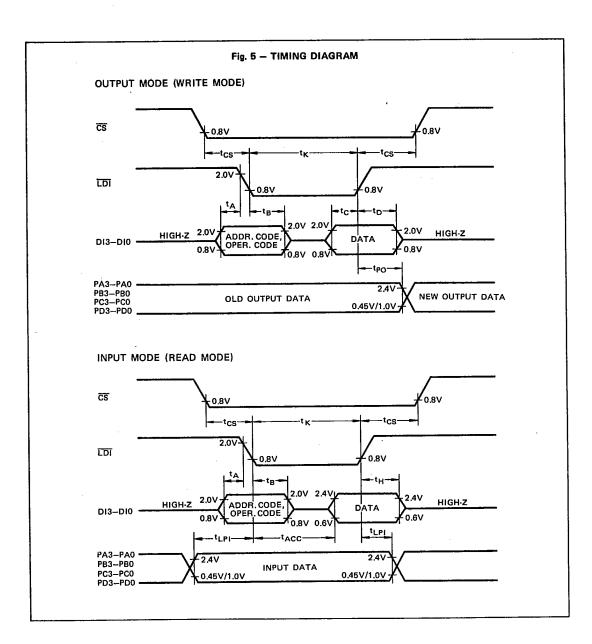

For interface to the MCU, the MB 88304 and MB 88305 have a 4-bit interface port (DI0 to DI3), a strobe input (\overline{LDI}\) pin), and a chip select input (\overline{CS}\) pin). The interface data consists of two 4-bit units. The first 4 bits give the operation code (2-bits) and address code (2 bits). The second 4-bits are the input or output data. Both 4-bit units are transferred through the interface port (DI0 to DI3) on timings determined by the strobe (\overline{LDI}\) signal. The MB 88304 or MB 88305 reads the operation code and address code from the MCU on the falling edge of the \overline{LDI}\) signal, and sends or receives the I/O data on the rising edge of \overline{LDI}\).

The  $\overline{\text{CS}}$  pin is used to read a chip select signal from the MCU's I/O port when two or more MB 88304 or MB 88305 chips are connected to the MCU.

| Ope. Code |        | -                                    | Addr | Code |                            |  |

|-----------|--------|--------------------------------------|------|------|----------------------------|--|

| DI3       | DI2    | Funciton                             | DII  | DIO  | Port Address               |  |

| 0         | 0      | IN (Input)<br>OUT (Output)           | 0    | 0    | Port A (PA)<br>Port B (PB) |  |

| 1         | 0<br>1 | OR (Logical OR)<br>AND (Logical AND) | 1    | 0    | Port C (PC)<br>Port D (PD) |  |

#### POWER ON RESET

The MB 88304 and MB 88305 contain an internal power-on reset circuit that detects the rise of  $V_{\rm CC}$  on the power supply line and holds the chip circuits in the reset state. In the reset state, the interface port (pins DI0 to DI3) is set to the input state, and ports A to D (PA to PD) are in the high-impedance state (except that latched output ports are not reset). The  $V_{\rm CC}$  line must rise smoothly for the reset circuit to operate. Regardless of the input level (high of low) of the  $\overline{\rm LDI}$  pin at the moment power is applied, the reset state is released at the first falling edge of the  $\overline{\rm LDI}$  input. A power-on reset also occurs if the supply voltage ( $V_{\rm CC}$ ) drops to 1 V or less, then recovers to the rated voltage.

#### **OUTPUT MODE (Write Mode)**

Corresponding to three functions of the MCU, the MB 88304 and MB 88305 have three output modes: data transfer output (OUT), logical OR (OR), and logical AND (AND).

#### OUT

The designated port latches and outputs the 4-bit data transferred from the MCU.

#### AND

The 4-bit data transferred from the MCU is ANDed with the 4-bit data of the designated port, which then latches the result as output.

#### • OR

The 4-bit data transferred from the MCU is ORed with the 4-bit data of the designated port, which then latches the result as output.

The operation code and address code sent from the MCU to pins DIO to DI3 of the MB 88304 or MB 88305 are latched on the falling edge of the strobe signal at the  $\overline{\text{LDI}}$  pin. The MCU data is read on the rising edge of the strobe signal and sent to the logic circuit of the designated port, where it is processed. The MCU data is then latched as output data.

#### INPUT MODE (Read Mode)

The MB 88304 and MB 88305 have only one input mode (IN), corresponding to data input by the MCU.

#### • IV

The input data at the port designated by the MCU is read and sent to the MCU via the interface port (DI0 to DI3).

The operation and address code sent from the MCU to pins DI0 to DI3 of the MB 88304 or MB 88305 are latched on the falling edge of the strobe signal at the LDI pin. If the operation code specifies input, the MB 88304 or MB 88305 sends data from the port designated by the address code to the MCU via DI0 to DI3.

A power-on reset places the chip in the input mode with ports A to D in the high-impedance state. If only the IN function is used thereafter, the ports remain in the high-impedance state. Release from the high-impedance state takes place when the OUT, AND, or OR function is used.

The MB 88304 and MB 88305 are designed for easy external driving. The MB 88304 has open-drain outputs, while the MB 88305 outputs have pull-up resistors. For both chips, the input level of a port to be used for input can be read by writing a 1 and performing the IN function. Input and output can therefore be intermixed within the four bits of each of the four ports (A to D).

FUJITSU MB 88304 MB 88305 IIIIIIIII

T-52-33-03

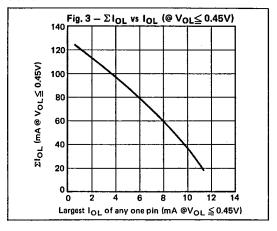

#### SINK CURRENT FROM PORTS A TO D

When  $\rm V_{OL} \leqq 0.45V$  , the MB 88304 and MB 88305 can sink 5mA (IOL) on each of their 16 I/O lines simultaneously. When this current sinking capability is not required on all of the I/O lines, or not all of the lines have to sink 5mA, the driving capability (sink current) of the other I/O lines can be increased according to the characteristics shown in the curve below.

For instance, if one of the I/O lines has to sink 9mA, the total  $I_{OL}$  ( $\Sigma\,I_{OL}$ ) of all the lines can be up to 45mA.

Example-1: How many I/O lines with 5 TTL leads can be driven?

$I_{OL} = 5 \times 1.6 \text{mA} = 8 \text{mA}$

$\Sigma I_{OL} \leq 60$  mA (from the total  $I_{OL}$  characteristics curve)

60mA/8mA = 7 I/O lines

The chip can drive 7 lines with 5 TTL loads, making a total of 56mA on these lines. The remaining 4mA can be shared among the other 9 I/O lines.

Example-2: Suppose that two of the load lines have  $I_{OL}$  = 20mA (at  $V_{OL} \le 1V$ ). Can the MB 88304 or MB 88305 drive the following loads?

2 I/O lines: 20mA (at  $V_{OL} \le 1V$ )

8 I/O lines: 4 mA (at  $V_{OL} \le 0.45 V$ )

6 I/O lines: 3.2mA (at V<sub>OL</sub> ≤ 0.45V)

Total I<sub>OL</sub> = (2x20mA) + (8x4mA) + (6x3.2mA)

= 91.2mA

Reading the total IOL characteristic for IOL = 4mA, we see that  $\Sigma I_{OL} \le 93$ mA. Since 91.2mA  $\le 93$ mA, the chip can drive these loads.

Note: The allowable total I<sub>OL</sub> (ΣI<sub>OL</sub>) depends on the maximum sink current of the lines for which  $V_{OL}$  must be equal to or less than 0.45V.

**FUJITSU** FUJITSU MB 88304 MB 88305 T-52-33-03

MB 88304 FUJITSU MB 88305

T-52-33-03

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter             | Symbol           | Rating                       | Unit |  |

|-----------------------|------------------|------------------------------|------|--|

| Supply Voltage        | V <sub>cc</sub>  | V <sub>SS</sub> -0.3 to +7.0 | V    |  |

| Input Voltage         | V <sub>IN</sub>  | V <sub>SS</sub> -0.3 to +7.0 | ٧    |  |

| Operating Temperature | TA               | -30 to +70                   | °c   |  |

| Storage Temperature   | T <sub>stg</sub> | -55 to +150                  | °c   |  |

| Power Dissipation     | P <sub>D</sub>   | 1.0                          | W    |  |

NOTE: Permanent device damage may occur if ABSOLUTE MAXI-MUM RATINGS are exceeded. MUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational section of this data sheet. Exposure to ABSOLUTE MAXIMUM RATINGS conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol          | Value      | Unit |  |

|-----------------------|-----------------|------------|------|--|

|                       | Vcc             | +5 ±10%    | ٧    |  |

| Supply Voltage        | V <sub>SS</sub> | 0          |      |  |

| Operating Temperature | TA              | -30 to +70 | °C   |  |

### DC CHARACTERISTICS ( $T_A = -30^{\circ}$ C to $+70^{\circ}$ C, $V_{CC} = +5$ V $\pm 10\%$ , $V_{SS} = 0$ V)

| Parameter                                           |                        | Combal           | Value                |      |                       | l Inia | Conditions                                          |  |

|-----------------------------------------------------|------------------------|------------------|----------------------|------|-----------------------|--------|-----------------------------------------------------|--|

|                                                     |                        | Symbol           | Min.                 | Тур. | Max.                  | Unit   | Conditions                                          |  |

| Input Low Voltage                                   |                        | VIL              | V <sub>SS</sub> -0.3 |      | 0.8                   | ٧      |                                                     |  |

| Input High Voltage                                  |                        | V <sub>IH</sub>  | 2.0                  |      | V <sub>cc</sub> + 0.3 | ٧      |                                                     |  |

| Output Low Voltage                                  | Port A to D            | V <sub>OL1</sub> | -                    |      | 0.45                  | ٧      | I <sub>OL</sub> = 5mA                               |  |

|                                                     |                        | V <sub>OL2</sub> | - 1                  |      | 1.0                   | ٧      | I <sub>OL</sub> = 20mA                              |  |

| Output Low Voltage                                  | DI0 to DI3             | V <sub>OL3</sub> | -                    |      | 0.6                   | ٧      | I <sub>OL</sub> = 1.8mA                             |  |

| Output High Voltage                                 | Ports A to D           | V <sub>OH1</sub> | 2.4                  |      |                       | . V    | I <sub>OH</sub> = -50μA (MB 88305)                  |  |

| Output High Voltage                                 | DI0 to DI3             | V <sub>OH2</sub> | 2.4                  |      |                       | ٧      | I <sub>OH</sub> = -100μA                            |  |

|                                                     | Ports A to D           | I <sub>IL1</sub> | -10                  |      | 20                    | μА     | $V_{SS} \leq V_{IN} \leq V_{CC}$                    |  |

| Input Leakage<br>Current                            | DIO to DI3,<br>CS, LDI | l <sub>IL2</sub> | -10                  |      | 10                    | μΑ     | V <sub>SS</sub> ≦ V <sub>IN</sub> ≦ V <sub>CC</sub> |  |

| Input Current                                       | Ports A to D           | 1,               |                      | 2.0  |                       | mΑ     | V <sub>IN</sub> = V <sub>SS</sub> (MB 88305)        |  |

| Total I <sub>OL</sub> Output Curr<br>from 16 Output | ent                    | ΣI <sub>OL</sub> |                      |      | 80                    | mA     | Each output current: 5mA                            |  |

| Supply Current                                      | V <sub>cc</sub>        | Icc              | 1                    | 10   | 24                    | mA     |                                                     |  |

FUJITSU MB 88304 MB 88305

## AC CHARACTERISTICS (T<sub>A</sub> = $-30^{\circ}$ C to $+70^{\circ}$ C, $V_{CC}$ = +5V ± 10%, $V_{SS}$ = 0V)

| Parameter                   |                               | Sumbal           | Value |      |      | T    |                        |

|-----------------------------|-------------------------------|------------------|-------|------|------|------|------------------------|

| raranietei                  | Sym                           | Symbol           | Min.  | Тур. | Max. | Unit | Condition              |

| Address/Op Codes Setup Time | DI3 to DI0                    | t <sub>A</sub>   | 100   |      |      | ns   | C <sub>L</sub> = 80pF  |

| Address/Op Codes Hold Time  | DI3 to DI0                    | t <sub>B</sub>   | 60    |      |      | ns   | C <sub>L</sub> = 20pF  |

| Data Setup Time             | DI3 to DI0<br>(Output Mode)   | tc               | 200   |      |      | ns   | C <sub>L</sub> = 80pF  |

| Data Hold Time              | DI3 to DI0<br>(Output Mode)   | t <sub>D</sub>   | 20    |      |      | ns   | C <sub>L</sub> = 20pF  |

| Data Output Delay Time      | Ports A to D<br>(Output Mode) | t <sub>PO</sub>  |       |      | 700  | ns   | C <sub>L</sub> = 100pF |

| LDI Pulse Width             | LDI                           | t <sub>K</sub>   | 700   |      |      | ns   |                        |

| CS Setup/Hold Time          | <u>cs</u>                     | t <sub>CS</sub>  | 50    |      |      | ns   |                        |

| Input Data Setup/Hold Time  | Ports A to D<br>(Output Mode) | t <sub>LPi</sub> | 100   |      |      | ns   |                        |

| Data Output Delay Time      | DI3 to DI0<br>(Input Mode)    | t <sub>ACC</sub> |       |      | 650  | ns   | C <sub>L</sub> = 80pF  |

| Data Hold Time              | DI3 to DI0<br>(Input Mode)    | t <sub>H</sub>   | 0     |      | 150  | ns   | C <sub>L</sub> = 20pF  |

T-52-33-03

P IP work

FUJITSU

FUJITSU MB 88304 MB 88305

## PACKAGE DIMENSIONS PLASTIC DIP (Suffix: -P)